## Journal Paper

# An extensible framework for multicore response time analysis

Robert Davis

Sebastian Altmeyer

Leandro Indrusiak

Claire Maiza

Vincent Nelis

Jan Reineke

**CISTER-TR-181110**

#### An extensible framework for multicore response time analysis

Robert Davis, Sebastian Altmeyer, Leandro Indrusiak, Claire Maiza, Vincent Nelis, Jan Reineke

\*CISTER Research Centre

Polytechnic Institute of Porto (ISEP-IPP)

Rua Dr. António Bernardino de Almeida, 431

4200-072 Porto

Portugal

Tel.: +351.22.8340509, Fax: +351.22.8321159

E-mail:

http://www.cister.isep.ipp.pt

#### **Abstract**

In this paper, we introduce a multicore response time analysis (MRTA) framework, which decouples response time analysis from a reliance on context-independent WCET values. Instead, the analysis formulates response times directly from the demands placed on different hardware resources. The MRTA framework is extensible to different multicore architectures, with a variety of arbitration policies for the common interconnects, and different types and arrangements of local memory. We instantiate the framework for single level local data and instruction memories (cache or scratchpads), for a variety of memory bus arbitration policies, including: Round-Robin, FIFO, Fixed-Priority, Processor-Priority, and TDMA, and account for DRAM refreshes. The MRTA framework provides a general approach to timing verification for multicore systems that is parametric in the hardware configuration and so can be used at the architectural design stage to compare the guaranteed levels of real-time performance that can be obtained with different hardware configurations. We use the framework in this way to evaluate the performance of multicore systems with a variety of different architectural components and policies. These results are then used to compose a predictable architecture, which is compared against a reference architecture designed for good average-case behaviour. This comparison shows that the predictable architecture has substantially better guaranteed real-time performance, with the precision of the analysis verified using cycle-accurate simulation.

### An extensible framework for multicore response time analysis

Robert I. Davis $^{1,2}$  · Sebastian Altmeyer $^3$  · Leandro S. Indrusiak $^1$  · Claire Maiza $^4$  · Vincent Nelis $^5$  · Jan Reineke $^6$

Published online: 18 July 2017

© The Author(s) 2017. This article is an open access publication

**Abstract** In this paper, we introduce a *multicore response time analysis (MRTA)* framework, which decouples response time analysis from a reliance on context-independent WCET values. Instead, the analysis formulates response times directly

This paper extends initial research on "A Generic and Compositional Framework for Multicore Response Time Analysis" presented at RTNS 2015 (Altmeyer et al. 2015).

The additional material includes: Section 4: analysis for warmed-up caches and dynamic scratchpads (Sects. 4.3 and 4.2). Section 7: extensions to the task model, including RTOS and interrupts, shared software resources, and open systems and incremental verification. Section 8: presentation of a cycle-accurate multicore simulator. Section 9: evaluation of different local memory types (Sect. 9.2), a comparison between predictable and reference architectures (Sect. 9.3), and a verification of the precision of the analysis using results from the simulator (Sect. 9.4).

⊠ Sebastian Altmeyer altmeyer@uva.nl

Robert I. Davis rob.davis@york.ac.uk

Leandro S. Indrusiak leandro.indrusiak@york.ac.uk

Claire Maiza claire.maiza@imag.fr

Vincent Nelis nelis@isep.ipp.pt

Jan Reineke reineke@cs.uni-saarland.de

- University of York, York, UK

- 2 INRIA Paris, Paris, France

- University of Amsterdam, Amsterdam, The Netherlands

from the demands placed on different hardware resources. The MRTA framework is extensible to different multicore architectures, with a variety of arbitration policies for the common interconnects, and different types and arrangements of local memory. We instantiate the framework for single level local data and instruction memories (cache or scratchpads), for a variety of memory bus arbitration policies, including: Round-Robin, FIFO, Fixed-Priority, Processor-Priority, and TDMA, and account for DRAM refreshes. The MRTA framework provides a general approach to timing verification for multicore systems that is parametric in the hardware configuration and so can be used at the architectural design stage to compare the guaranteed levels of real-time performance that can be obtained with different hardware configurations. We use the framework in this way to evaluate the performance of multicore systems with a variety of different architectural components and policies. These results are then used to compose a predictable architecture, which is compared against a reference architecture designed for good average-case behaviour. This comparison shows that the predictable architecture has substantially better guaranteed real-time performance, with the precision of the analysis verified using cycle-accurate simulation.

**Keywords** Multicore scheduling · Timing analysis · Verification

#### 1 Introduction

Effective analysis of the worst-case timing behaviour of systems built on multicore architectures is essential if these high-performance platforms are to be deployed in critical real-time embedded systems used in the automotive and aerospace industries. We identify four different approaches to solving the problem of determining timing correctness.

With single-core systems, a *traditional two-step* approach is typically used. This consists of timing analysis which determines the *context-independent* worst-case execution time (WCET) of each task, followed by schedulability analysis, which uses task WCETs and information about the processor scheduling policy to determine if each task can be guaranteed to meet its deadline. When local memory (e.g. cache) is present, then this approach can be augmented by analysis of Cache Related Preemption Delays (CRPD) (Altmeyer et al. 2012), or by partitioning the cache to avoid CRPD altogether. Both approaches are effective and result in tight upper bounds on task response times (Altmeyer et al. 2014, 2016).

With a multicore system, the situation is more complex since WCETs are strongly dependent on the amount of *cross-core interference* on shared hardware resources such as main memory, L2 caches, and common interconnects, due to tasks running on other cores. The uncertainty and variability in this cross-core interference renders the traditional two-step process ineffective for many multicore processors. For exam-

<sup>&</sup>lt;sup>6</sup> Saarland University, Saarland Informatics Campus, Saarbrücken, Germany

<sup>&</sup>lt;sup>4</sup> Universite Grenoble-Alpes, Grenoble, France

<sup>&</sup>lt;sup>5</sup> CISTER, ISEP, Porto, Portugal

ple, on the Freescale P4080, the latency of a read operation varies from 40 to 600 cycles depending on the total number of cores running and the number of competing tasks (Nowotsch et al. 2014). Similarly, a 14 times slowdown has been reported (Radojković et al. 2012) due to interference on the L2 cache for tasks running on Intel Core 2 Quad processors. Further, recent work by Valsan et al. (2016) has shown that in some multicore systems with out-of-order execution, cache partitioning is insufficient to provide effective isolation, with shared Miss Status Handling Registers (MSHR) causing up to 20 times slowdown to code allocated its own separate cache partition.

At the other extreme is a *fully integrated* approach. This involves considering the precise interleaving of instructions originating from different cores (Gustavsson et al. 2010); however, such an approach suffers from potentially insurmountable problems of combinatorial complexity, due to the proliferation of different path combinations, as well as different release times and schedules.

An alternative approach is based on *temporal isolation* (Bui et al. 2011). The idea here is to statically partition the use of shared resources, e.g. space partitioning of cache and DRAM banks, time partitioning of bus access etc., so that context-independent WCET values can be used and the traditional two-step process applied. This approach raises a further challenge, how to partition the resources to obtain schedulability (Reineke and Doerfert 2014). Techniques which seek to limit the worst-case cross-core interference, for example by using TDMA arbitration on the memory bus or by limiting the amount of contention by suspending execution on certain cores (Nowotsch et al. 2014), can have a significant detrimental effect on performance, effectively negating the performance benefits of using a multicore system altogether. We note that TDMA is rarely if ever used as a bus-arbitration policy in real multicore processors, since it is not work-conserving and so wastes significant bandwidth. This impacts both worst-case and average-case performance, which are essential for application areas such as telecommunications that have a major influence on processor design.

The final approach is the one presented in this paper, based on *explicit interference modelling*. We argue that the strong interdependencies between timing analysis and schedulability analysis on multicore systems lead to undue pessimism. Thus a more nuanced and expressive interface is needed to integrate the demands placed on different resources by each task into schedulability analysis. In our approach, we omit the notion of WCET per se and instead directly target the calculation of task response times based on the demands that tasks place on the different hardware resources.

In this work, as a proof of concept, we use execution traces to model the behaviour of tasks and their resource demands. Traces provide a simple yet expressive way to model task behaviour, that captures information about the sequence of instructions and their memory accesses and corresponding types (read/write). Note that relying on execution traces does not pose a fundamental limitation to our approach as all required parameters can also be derived using static analysis (Li and Malik 1995; Ferdinand et al. 1999; Altmeyer 2013); however, traces enable a simple analysis of resource demands and so allow us to focus on an integrated response time analysis for multicore systems.

The main parameters used are the processor demand and the memory demand of each task. The latter quantity is used in analysis of the arbitration policy for the common interconnect, enabling us to upper bound the total memory access delays which may occur during the response time of a task. By computing the overall processor demand and memory demand over a relatively long interval of time (i.e. the task response time), as opposed to summing the worst case over many short intervals (e.g. individual memory accesses), we are able to obtain much tighter response time bounds.

The Multicore Response Time Analysis framework (MRTA) that we present is extensible to different types and arrangements of local memory, and different arbitration policies for the common interconnect. We instantiate the MRTA framework assuming the local memories used for instructions and data are single-level and either cache, scratchpad, or not present. In the case of caches we consider both cold caches, i.e. execution from an empty cache, and warm caches, taking advantage of information that resides in the cache from previous execution. With scratchpads, we consider both static and dynamic behaviour. Further, we assume that the memory bus arbitration policy may be TDMA, FIFO, Round-Robin, Fixed-Priority (based on task priorities), or Processor-Priority. We also account for the effects of DRAM refresh (Atanassov and Puschner 2001; Bhat and Mueller 2011). The general approach embodied in the MRTA framework is extensible to more complex, multi-level memory hierarchies, and to other sources of interference. We outline how the framework and analysis can be adapted to cover interference due to operation of the real-time operating system (RTOS) and Interrupt Handlers, we also discuss how to take into account the effects of policies used to control access to shared software resources, and how the framework can be used with open systems and for incremental verification.

The MRTA framework provides a general timing verification framework that is parametric in the hardware configuration (common interconnect, local memories, number of cores, etc.) and so can be used at the architectural design stage to compare the guaranteed levels of real-time performance that can be obtained with different hardware configurations, and also during the development and integration stages to verify the timing behaviour of a specific system. We use the framework in this way to evaluate guaranteed performance for multicore systems with a variety of different architectural components and policies. These results are then used to compose a predictable architecture, which is compared against a reference architecture designed for good average-case behaviour. This comparison shows that the predictable architecture has substantially better guaranteed real-time performance, with the precision of the analysis verified using cycle-accurate simulation.

While the specific hardware models and their mathematical representations used in this paper cannot capture all of the interference and complexity of actual hardware, they serve as a valid starting point. They include the dominant sources of interference and represent current architectures reasonably well.

#### 1.1 Organisation

The rest of the paper is organised as follows. Section 2 discusses the related work. Section 3 describes the system model and notation used. Sections 4 and 5 show

how the effects of a local memory and the common interconnect can be modelled. Section 6 presents the nucleus of our framework, interference-aware MRTA. This analysis integrates processor and memory demands accounting for cross-core interference. Extensions to the presented analysis are discussed in Sect. 7. Section 8 describes a cycle-accurate simulator used to verify the precision of the analysis. Section 9 provides the results of an experimental evaluation using the MRTA framework, and Sect. 10 concludes with a summary and perspectives on future work.

#### 2 Related work

The problem of estimating the response time of software real-time tasks executed on a multicore architecture is not new. The research community has been active in this area for the past ten years and an array of solutions have been proposed. Most of these solutions are, however either single-point solutions applicable to specific software and hardware models, or they focus exclusively on one particular sub-problem and abstract the rest by making simplistic assumptions. Only a few research works aim at designing a holistic analysis technique, typically because the solutions specific to the various sub-problems are very difficult to combine.

We note that it is challenging to organize the related work, since it is rare to find papers that share the same assumptions about the application and the hardware model. We therefore make a simple classification based on the primary focus of the analysis, whether it is on interference at the shared cache, memory bus, or main memory level, or on parameterizing WCETs. Further works are also covered that assume distinct application models and hardware models.

#### 2.1 Related work with a focus on the memory bus

Although listed in this category, some of the works cited below also consider interference at the cache(s) or main memory level as well. However, they typically make either pessimistic or simplistic assumptions (like having private caches only) at those levels in order to simplify the model and thus focus on the contention for the shared memory bus.

Rosen et al. (2007) proposed an analysis technique for systems in which the shared memory bus uses TDMA arbitration and the time slots are statically assigned to the cores. This technique relies on (i) the availability of a user-programmable table-driven bus arbiter, which is typically not available in real hardware, and (ii) on the knowledge at design time of the characteristics of the entire workload that executes on each core.

In the same vein, also relying on TDMA arbitration of the memory bus, Chattopadhyay et al. (2010) and Kelter et al. (2011) proposed a response time analysis technique that considers a shared bus and an instruction cache, assuming separate buses and memories for both code and data. Their methods have limited applicability though, as they do not address data accesses to memory.

Paolieri et al. (2009) proposed a *multicore architecture* with hardware that enforces a constant upper bound on the latency of each access to a shared L2 memory through a shared bus. This approach enables the analysis of tasks in isolation since the interference on other tasks can be conservatively accounted for using this bound on the latency of each access. Similarly, the PTARM (Liu et al. 2012) enforces constant latencies for all instructions, including loads and stores; however, both cases represent customized hardware.

Lv et al. (2010) used *timed automata* to model the memory bus and the memory request patterns. Their method handles instruction accesses only and may suffer from state-space explosion when applied to data accesses. Another method employing timed automata was proposed by Gustavsson et al. (2010) in which the WCET is obtained by proving special predicates through model checking. This approach enables detailed system modelling, but is also prone to the problem of state-space explosion.

Schliecker et al. (2010) proposed a method that employs a *general event-based model* to estimate the maximum load on a shared resource. This approach makes few assumptions about the task model and is thus quite generally applicable; however, it only supports a single unspecified work-conserving bus arbiter.

Yun et al. (2012) proposed a *software-based memory throttling mechanism* to explicitly limit the memory request rate of each core and thereby control the memory interference. They also developed analytical solutions to compute proper throttling parameters that ensure the schedulability of critical tasks while minimising the performance impact of throttling.

Kelter et al. (2014) analysed the maximum bus arbitration delays for multicore systems sharing a TDMA bus and using both (private) L1 and (shared) L2 instruction and data caches.

Dasari et al. (2016) proposed a general framework to compute the maximum interference caused by the shared memory bus and its impact on the execution time of the tasks running on the cores. This method is more complex than the one proposed in this paper, and may be more accurate when it estimates the delay due to the shared bus; however, it assumes partitioned caches and therefore does not take cacherelated effects into account, which makes it less general than the framework proposed here.

Jacobs et al. (2016) proposed a formal framework for the derivation of sound WCET analyses for multi-core processors. They show how to apply their analysis to account for interference on shared buses, accounting for cumulative information about the interference from tasks on other cores.

Huang et al. (2016) presented a response-time analysis that applies to multicores with one shared resource under fixed-priority arbitration. They give a simple task-to-core allocation algorithm and show that in conjunction with their response-time analysis it has a speedup factor of 7. Unlike the work in this paper, their model neither accounts for cache-related pre-emption delays nor for DRAM refreshes. Huang et al. (2016) also provide an improved response-time analysis for the case where tasks suspend from their processing core when accessing a shared resource. This is a reasonable assumption for DMA transfers, but not for individual memory accesses.

#### 2.2 Related work with a focus on main memory

Most of the related work on memory controllers proposes scheduling algorithms that improve the controller performance, i.e., the average time to serve a sequence of requests, by (re)ordering the incoming requests at the controller level. Typically, these techniques are aimed at reducing the number of transitions between read and write modes. They seek to get the best performance from an open page policy by exploiting data locality.

Targeting real-time systems and thus time-predictability rather than performance, Kim et al. (2014a, 2016) presented a model to upper bound the memory interference delay caused by concurrent accesses to shared DRAM. Their work differs from this paper in that they primarily focus on the contention at the DRAM controller, assuming either fully-partitioned private caches or shared caches. For shared caches, they simply assume that either task preemption does not incur cache-related preemption delays (assuming in this case that cache coloring mechanisms are employed), or that the extra number of memory requests resulting from cache line evictions at runtime is given. Any further delays from shared resources, such as the memory bus, are simply assumed to be accounted for in the tasks' WCETs.

#### 2.3 Related work with a focus on shared caches and scratchpads

Regarding the problem of estimating the WCET of tasks running in systems with shared caches, Yan and Zhang (2008) proposed a solution assuming direct-mapped, shared L2 instruction caches on multicores. The applicability of the approach is unfortunately limited as it makes very restrictive assumptions such as (i) data caches are perfect, i.e. all accesses are hits, and (ii) data references from different threads will not interfere with each other in the shared L2 cache.

Li et al. (2009a) proposed a method to estimate the worst-case response time of concurrent programs running on multicores with shared L2 caches, assuming set-associative instruction caches using the LRU replacement policy. Their work was later extended by Chattopadhyay et al. (2010) by adding a TDMA bus analysis technique to bound the memory access delay.

Regarding flash memory, Li and Mayer (2016) proposed a post-processing analysis methodology to acquire precise information about task flash memory contentions based on non-intrusive traces. For scratchpad memory, most of the works aim at reducing the WCET by proposing optimized stack management techniques (Lu et al. 2013) or dynamic code management techniques (Kim et al. 2014b), for loading program code from the main memory to the scratchpad.

Considering shared caches, there are a plethora of works that aim at reducing the impact of task pre-emptions and hence also the cache related pre-emption delays. Solutions to that problem are various: some address the problem at the task scheduling level Davis et al. (2013, 2015) by adding restrictions on the time at which tasks may be pre-empted, or at the cache management policy level (Ward et al. 2013; Mancuso et al. 2013; Slijepcevic et al. 2014). It is outside the scope of this paper to discuss all these research works.

#### 2.4 Related work with a focus on parameterized WCETs

Rather than computing a unique upper-bound on the tasks' context independent WCET, some works propose solutions to characterize the WCET as a function of the platform characteristics and environment.

Paolieri et al. (2011) introduced an interference-aware task allocation algorithm that considers a set of WCET estimations per task, where each WCET estimation corresponds to a different execution environment (e.g. number of contending cores in a multicore system). The sensitivity of the WCET estimates to changes in the execution environment is used to guide the task to core allocation.

Reineke and Doerfert (2014) introduced *architecture-parametric* WCET analysis, which determines a function that bounds a task's WCET in terms of the amount and speed of resources allocated to that task. If a temporal-isolation approach is taken then such an analysis is required to partition shared resources in an informed manner. This analysis can also be adapted to determine WCET bounds in terms of the amount of interference on shared resources.

#### 2.5 Related work assuming different application models

Most of the related work assumes independent tasks and only a few approaches have been proposed so far that consider task dependencies to some extent. Among them, the approach proposed by Li et al. (2009b) analyzes the worst-case cache access scenario of parallelized applications modeled by Message Sequence Graphs. The approach suffers from a very high time-complexity and assumes that the cache access behaviors are known and finite. Choi et al. (2016) used a more general model, comprising an event stream model for resource access and a task graph model for dependent tasks, in order to support a wider range of resource access patterns and parallelized execution of an application.

Schranzhofer et al. (2010) developed a framework based on a TDMA-arbitrated bus. This was followed by work on resource adaptive arbiters (Schranzhofer et al. 2011). Their work assumes a task model where each task consists of sequences of super-blocks, themselves divided into phases that represent implicit communication (fetching or writing of data to/from memory), computation (processing the data), or both. In contrast to the techniques presented in this paper, their approach requires major program intervention and compiler assistance to prefetch data. Adopting a similar model, Pellizzoni et al. (2010) compute an upper bound on the contention delay incurred by periodic tasks, for systems comprising any number of cores and peripheral buses sharing a single main memory. Their method does not cater for sporadic tasks and does not apply to systems with shared caches. In addition it relies on accurate profiling of cache utilization, suitable assignment of the TDMA timeslots to the tasks' super-blocks, and imposes a restriction on where the tasks can be pre-empted.

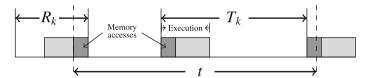

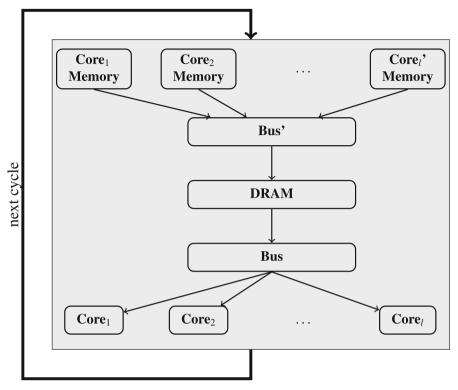

Pellizzoni et al. (2011) introduced the PRedictable Execution Model (PREM) framework. This framework considers tasks as consisting of memory phases where they pre-fetch instructions and data, and execution phases where they execute with-

out the need to access memory or I/O devices. The aim is to enable more efficient operation whereby the memory phase of one task overlaps with the execution phase of another. Yao et al. (2012) presented a TDMA scheduling algorithm for PREM tasks on a multicore, and Wasly and Pellizzoni (2014) provided schedulability analysis for non-preemptable PREM tasks on a partitioned multicore. Lampka et al. (2014) proposed a formal approach for bounding the worst-case response time of concurrently executing real-time tasks under resource contention and almost arbitrarily complex resource arbitration policies, with a focus on main memory as a shared resource. Global scheduling of PREM tasks has also been considered by Alhammad and Pellizzoni (2014) and Alhammad et al. (2015).

#### 2.6 Related work assuming COTS hardware components

COTS multicore processors are typically designed to optimize average-case performance and most of their internal mechanisms are usually not documented. For such multicore platforms, Yun et al. (2015) proposed a worst-case memory interference delay analysis under the assumptions that (i) multiple memory requests can be simultaneously outstanding and (ii) the COTS DRAM controller has a separate read and write request buffer, prioritizes reads over writes, and supports out-of-order request processing. In contrast with this work, they assume non-blocking caches (common in COTS processors) that can handle multiple simultaneous cache-misses and focus solely on non-shared LLC (last level of cache) and DRAM bank partitioned systems. Non blocking caches have been the focus a multiple studies recently; however, we do not cover those techniques here. The main problem with non-blocking caches is that the miss status holding registers (MSHRs), special hardware registers which track the status of outstanding cache-misses, can be a significant source of contention (Valsan et al. 2016).

Trilla et al. (2016) proposed a timing model to predict the performance of applications at an early design stage. Their approach is based on generating an execution profile for each application that allows contention analysis on the shared processor resources. The main difference with our approach resides in their assumption that most of the hardware arbitration mechanisms are undocumented and therefore the applications' execution profiles are obtained based on an empirical analysis.

Most work on response time analysis for multicores, including this paper, assumes *timing compositionality* (Hahn et al. 2013). Intuitively, for a timing-compositional multicore, it is safe to separately account for delays from different sources, such as computation on a given core, additional cache misses due to preemptions, and interference on a shared bus. Unfortunately, recent results by (Hahn et al. 2015) indicate that even simple commercial multicores are non-compositional, rendering most existing analyses unsound for these architectures. Hahn et al. (2016), however, introduced an extended WCET analysis that enables compositional response time analysis for arbitrary, non-compositional multicores.

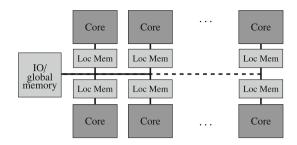

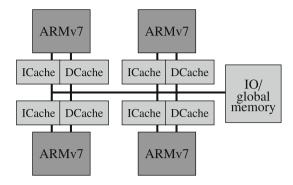

Fig. 1 Multicore platform. A set of  $\ell$  cores with local memories connected via a common bus to a global memory

#### 3 System model

In this paper, we provide a theoretical framework that can be instantiated for a range of different multicore architectures with different types of memory hierarchy and different arbitration policies for the common interconnect. Our aim is to create a flexible, adaptable, and generic analysis framework wherein a large number of common multicore architecture designs can be modeled and analysed. Inevitably, in this paper we can only cover a limited number of types of local memory, bus, and global memory behaviour. We select common approaches to model the different hardware components and integrate them into an extensible framework.

#### 3.1 Multicore architectural model

We model a generic multicore platform with  $\ell$  timing-compositional cores  $P_1, \ldots P_\ell$  as depicted in Fig. 1. By timing-compositional cores we mean cores where it is safe to separately account for delays from different sources, such as computation on a given core and interference on a shared bus (Hahn et al. 2013).

The set of cores is defined as  $\mathbb{P}$ . Each core has a local memory which is connected via a shared bus to a global memory and IO interface. We assume constant delays  $d_{\text{main}}$  to retrieve data from global memory under the assumption of an immediate bus access, i.e., no wait-cycles or contention on the bus. We assume atomic bus transactions, i.e., no split transactions, which furthermore are not re-ordered, and non-preemptable busy waiting on the core for requests to be serviced. Further, we assume that bus access may be given to cores for one access at a time. The types of the memories and the bus policy are parameters that can be instantiated to model different multicore systems.

In this paper we assume write-through caches only and omit consideration of delays due to cache coherence and synchronization. We also consider write-through and write-back scratchpads.

#### 3.2 Task model

We assume a set of n sporadic tasks  $\{\tau_1, \ldots, \tau_n\}$ ; each task  $\tau_i$  has a minimum period or inter-arrival time  $T_i$  and a deadline  $D_i$ . Deadlines are assumed to be constrained, hence  $D_i \leq T_i$ .

We assume that the tasks are statically partitioned to the set of  $\ell$  identical cores  $\{P_1, \ldots, P_\ell\}$ , and scheduled on each core using fixed-priority pre-emptive scheduling. The set of tasks assigned to core  $P_x$  is denoted by  $\Gamma_x$ .

The index of each task is unique and thus provides a global priority order, with  $\tau_1$  having the highest priority and  $\tau_n$  the lowest. The global priority of each task translates to a local priority order on each core which is used for scheduling purposes. We use hp(i) (lp(i)) to denote the set of tasks with higher (lower) priority than that of task  $\tau_i$ , and we use hp(i) (lep(i)) to denote the set of tasks with higher or equal (lower or equal) priority to task  $\tau_i$ .

We initially assume that the tasks are independent, in so far as they do not share mutually exclusive software resources (discussed in Sect. 7); nevertheless, the tasks compete for hardware resources such as the processor core, local memory, and the memory bus.

The execution of task  $\tau_i$  is modelled using a set of traces  $O_i$ , where each trace  $o = [\iota_1, \ldots \iota_k]$  is an ordered list of instructions. For ease of notation, we treat the ordered list of instructions as a multi-set, whenever we can abstract away from the specific order. We distinguish three types of instruction it:

$$it = \begin{cases} r[m^{da}] & \text{read data from memory block } m^{da} \\ w[m^{da}] & \text{write data to memory block } m^{da} \\ e & \text{execute} \end{cases}$$

(1)

An instruction  $\iota$  is a triple consisting of the instruction's memory address  $m^{\rm in}$ , its execution time  $\Delta$  without memory delays, i.e., assuming a perfect local memory, and the instruction type it:

$$\iota = (m^{\rm in}, \Delta, it) \tag{2}$$

We use m to denote a memory block, and the set of memory blocks is defined as  $\mathbb{M}$ .  $\mathbb{M}^{\text{in}}$  denotes the instruction memory blocks and  $\mathbb{M}^{\text{da}}$  the data memory blocks.  $m^{\text{in}}$  and  $m^{\text{da}}$  are defined accordingly. We assume that data memory and instruction memory are disjoint, i.e,  $\mathbb{M}^{\text{in}} \cap \mathbb{M}^{\text{da}} = \emptyset$ .

#### 3.2.1 Using traces to model the tasks' behaviour

The use of traces to model a task's behaviour is unusual as the number of traces is exponential in the number of control-flow branches. Despite this obvious drawback, we decided to use traces for a number of reasons:

- Traces provide a simple yet expressive way to model task behaviour. They enable

a near-trivial static cache analysis and a simple multicore simulation to evaluate

the accuracy of the timing verification framework.

- Traces show that the worst-case execution behaviour of a task  $\tau_i$  on a multicore system is *not* uniquely defined. For example, the highest impact on a task scheduled on the same core due to task  $\tau_i$  may occur when it uses that core for the longest possible time interval, whereas the highest impact on tasks scheduled on other cores may occur when task  $\tau_i$  produces the largest number of bus accesses. These two cases may well correspond to different execution traces.

As a remedy for the exponential number of traces, complexity can be reduced by (i) computing a synthetic worst-case trace or by (ii) deriving the set of Pareto optimal traces that maximize the task's impact on a given performance metric or combination of different performance metrics, see (Li and Malik 1995). (The derivation of the Pareto front of traces is part of our future work.)

We note that using traces does not reduce the applicability of our approach. We use traces as a simple model which allows us to describe the computation of resource demand for various types of architectural component, and to focus on the multicore response time analysis. We can also completely resort to static analysis to derive independent upper bounds on the resource demands. For example, a static cache analysis (Ferdinand et al. 1999) can be used to bound the number of bus and also DRAM accesses. Static pre-emption cost analyses (Altmeyer 2013) are also available to bound the impact of pre-emptions, and we can use implicit path enumeration (Li and Malik 1995) to derive an upper bound on the purely computational demand of a task. These independently derived upper bounds can then be represented by a single, synthetic trace that maximizes each type of resource demand. Using static analyses in this way strongly reduces the computational complexity, but may lead to pessimism. These static analyses are, however, outside the scope of this paper, and an evaluation of the trade-off in terms of pessimism is left for future work.

#### 3.3 Pre-emption cost model

We now extend the task model introduced above to include pre-emption costs. These costs occur when the pre-empting task evicts cache blocks of the pre-empted task that have to be reloaded after the pre-empted task resumes. To analyse the effect of pre-emption on a pre-empted task, Lee et al. (1998) introduced the concept of a useful cache block. Applying this concept to traces, a memory block m is referred to as a useful cache block (UCB) at a program point corresponding to instruction  $\iota$  on trace o, if (i) m is cached at that program point and (ii) m is reused by a later instruction in the trace without prior eviction. In the case of pre-emption at the program point corresponding to instruction  $\iota$  on trace o, only the memory blocks that (i) are cached and (ii) will be reused, may cause additional reloads. Hence, the number of UCBs at a program point gives an upper bound on the number of additional reloads due to a pre-emption at that point in the trace. A tighter definition is presented by Altmeyer and Burguière (2009); however, in this paper we need only the basic concept.

The worst-case impact of a pre-empting task is given by the number of cache blocks that the task may evict during its execution. A memory block accessed during the execution of a trace o is referred to as an evicting cache block (*ECB*). Accessing an ECB may evict a cache block of a pre-empted task. The intersection of UCBs of the pre-empted tasks with ECBs of the pre-empting task provides a tight upper bound on the cache-related pre-emption costs.

In this paper, we represent the sets of ECBs and UCBs as sets of integers with the following meaning:

$s \in UCB_{t,o} \Leftrightarrow$  the program point t in trace o has a useful cache block in cache-set s  $s \in ECB_o \Leftrightarrow$  trace o may evict a cache block in cache-set s

We note that a separate computation of the pre-emption cost is restricted to architectures without timing anomalies (Lundqvist and Stenström 1999) but is independent of the type of cache used, i.e. data, instruction or unified cache. For examples of the use of UCBs and ECBs to compute pre-emption costs, see the work of Altmeyer et al. (2012).

#### 3.4 Table of notation

Table 1 provides a quick reference for the notation used in this paper. Much of this notation is introduced and defined in later sections. Note we do not include in this table notation that is only used locally for the purpose of simplifying expressions.

#### 4 Memory modelling

In this section we show how the effects of a local memory can be modelled via a MEM function which describes the number of accesses due to a task which are passed to the next level of the memory hierarchy, in this case main memory. The MEM function is instantiated for both cache and scratchpads. We model the effect of a (local) memory using a function of the form:

$$MEM: \mathbb{O} \to \mathbb{N} \times 2^{2^{\mathbb{N}}} \times 2^{\mathbb{N}}$$

(3)

where  $\mathbb{O}$  is the domain of traces and MEM(o) = (MD $_o$ ,  $\overline{\text{UCB}}_o$ , ECB $_o$ ) computes, for a trace o, three quantities: (i) the number of bus accesses i.e., the number of memory accesses which cannot be served by the local memory alone, referred to as the memory demand MD $_o$ ; (ii) a multiset  $\overline{\text{UCB}}_o$  containing, for each program point  $\iota$  in trace o, the set of Useful Cache Blocks (UCBs), which may need to be reloaded when trace o is pre-empted at that program point, i.e.  $\overline{\text{UCB}}_o = \bigcup_{\iota \in o} \{\text{UCB}_{\iota o}\}$ ; (iii) the set ECB $_o$  of Evicting Cache Blocks (ECBs) corresponding to the set of all cache blocks accessed by trace o which may evict memory blocks of other tasks from the cache. MD does not just cover cache misses, but also has to account for write accesses. In the case of write-through caches, each write access will cause a bus access, irrespective of whether or not the memory block is present in cache. (We leave integration of analysis for write-back caches (Davis et al. 2016) as future work).

MD assumes non-preemptive execution. With pre-emptive execution and caches, more than MD memory accesses can contribute to the bus contention. In this paper, we make use of the CRPD analysis for fixed-priority pre-emptive scheduling introduced by Altmeyer et al. (2012) to upper bound the additional memory accesses needed to reload cache blocks evicted due to pre-emption.

We now derive instantiations of the function MEM(o) for a trace  $o = [\iota_1, \ldots, \iota_k]$  for instruction memories and data memories for systems (i) without cache, (ii) with

| Table 1 Notation                                                   |                                                                                                |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Set of cores                                                       | $\mathbb{P} = \{P_1, \dots, P_\ell\}$                                                          |

| Number of cores                                                    | $\ell$                                                                                         |

| Core index                                                         | x,y                                                                                            |

| Task set                                                           | $\Gamma = \{\tau_1, \ldots, \tau_n\}$                                                          |

| Number of tasks                                                    | n                                                                                              |

| Task index                                                         | i,j                                                                                            |

| Tasks on core $P_X$                                                | $\Gamma_{\chi}$                                                                                |

| Task worst-case execution time with no interference                | $C_i$                                                                                          |

| Task period                                                        | $T_i$                                                                                          |

| Task deadline                                                      | $D_i$                                                                                          |

| Task response time                                                 | $R_i$                                                                                          |

| Task memory demand                                                 | $\mathrm{MD}_i$                                                                                |

| Task processor demand                                              | $PD_i$                                                                                         |

| Tasks with higher priority than $\tau_i$                           | hp(i)                                                                                          |

| Tasks with higher or equal priority to $\tau_i$                    | hep(i)                                                                                         |

| Tasks with lower priority than $\tau_i$                            | lp(i)                                                                                          |

| Tasks with lower or equal priority to $\tau_i$                     | lep(i)                                                                                         |

| Tasks $	au_j$ may pre-empt within the response time of $	au_i$     | aff(i, j)                                                                                      |

| Bus accesses from tasks in hep( $i$ ) on core $P_x$ in time $t$    |                                                                                                |

| Where $\tau_i$ is the task under analysis                          | $S_i^x(t)$                                                                                     |

| Bus accesses from tasks in $hep(j)$ on core $P_y$ in time $t$      | $A_j^y(t)$                                                                                     |

| Bus accesses from tasks in $lp(j)$ on core $P_y$ in time $t$       | $L_j^y(t)$                                                                                     |

| Memory block                                                       | m                                                                                              |

| Set of memory blocks                                               | M                                                                                              |

| Instruction type                                                   | $it = \begin{cases} r[m] \\ w[m] \\ e \end{cases}$                                             |

| Instruction                                                        | $\iota = (m, \Delta, it)$                                                                      |

| Execution trace                                                    | $o = [\iota_1, \dots \iota_k]$                                                                 |

| Set of traces of task $\tau_i$                                     | $O_i$                                                                                          |

| Memory demand of trace o                                           | $\mathrm{MD}_o$                                                                                |

| ECBs of trace o                                                    | $ECB_{O}$                                                                                      |

| ECBs of task $\tau_i$                                              | $ECB_i$                                                                                        |

| UCBs at instruction $\iota$ of trace $o$                           | $\mathit{UCB}_{\iota,o}$                                                                       |

| Multi-set of UCBs of trace o                                       | $\overline{	ext{UCB}}_o$                                                                       |

| Memory blocks cached after executing trace o                       | Cached(o)                                                                                      |

| Cache lines that may be evicted by tasks other than $\tau_i$       | POT-EVICTED $_i$                                                                               |

| Definitely cached memory blocks at the start of $	au_i$            | $DEF	ext{-}CACHED_i$                                                                           |

| Cost of a pre-emption by $\tau_j$ during response time of $\tau_i$ | $\gamma_{i,j,x}$                                                                               |

| Bus function                                                       | $\overline{\mathrm{BUS}} \colon \mathbb{N} \times \mathbb{P} \times \mathbb{N} \to \mathbb{N}$ |

| Memory function                                                    | $MEM: \mathbb{O} \to \mathbb{N} \times \mathbb{N} \times 2^{\mathbb{N}} \times 2^{\mathbb{N}}$ |

#### Table 1 continued

| Scratchpad function                                               | $SPM: \mathbb{M} \to \{true, false\}$                   |

|-------------------------------------------------------------------|---------------------------------------------------------|

| Cache hit function                                                | $Hit: \mathbb{I} \times \mathbb{M} \to \{true, false\}$ |

| Number of bus access slots assign to each core                    | v                                                       |

| Global memory delay                                               | $d_{main}$                                              |

| DRAM refresh delay                                                | $d_{ m refresh}$                                        |

| DRAM refresh period                                               | $T_{ m refresh}$                                        |

| Processor interference on task $\tau_i$ on core $P_x$ in time $t$ | $I^{\text{PROC}}(i, x, t)$                              |

| Bus interference on task $\tau_i$ on core $P_x$ in time $t$       | $I^{\mathrm{BUS}}(i,x,t)$                               |

| DRAM interference on task $\tau_i$ on core $P_x$ in time $t$      | $I^{\mathrm{DRAM}}(i,x,t)$                              |

|                                                                   |                                                         |

scratchpads, and (iii) with direct-mapped or LRU caches. In the following, the super-scripts indicate data (da) or instruction memory (in), and the subscripts the type of memory, i.e., uncached (nc), scratchpad (sp), or caches (ca).

#### 4.1 Uncached

Assuming a system with no cache, considering instruction memory, the number of bus accesses  $MD_o$  for a trace o is given by the number of instructions k in the trace. The sets of UCBs and ECBs are empty, as pre-emption has no effect on the performance of the local memory, since there is none.

$$MEM_{nc}^{in}(o) = (k, \emptyset, \emptyset)$$

(4)

Considering data memory, we have to account for the number of data accesses, irrespective of whether they are read or write accesses. The number of accesses  $MD_o$  is thus equal to the number of data access instructions.

$$\mathrm{MEM}_{\mathrm{nc}}^{\mathrm{da}}(o) = \left( \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, r/w[m^{\mathrm{da}}]) \right\} \right|, \emptyset, \emptyset \right)$$

(5)

#### 4.2 Scratchpads

Scratchpads are explicitly managed local memories that exhibit higher predictability and less dynamic behavior than caches. Hence, scratchpads are commonly advocated for embedded multicore systems.

Scratchpads can implement a write-back or, less commonly, a write-through policy for write accesses. Furthermore scratchpad management may be either static or dynamic. With a static scratchpad management, the scratchpad contents remain constant throughout operation, whereas with dynamic scratchpad management, scratchpad blocks can be reloaded as needed, for example on pre-emptions, which makes better use of the available scratchpad memory (Whitham et al. 2012, 2014).

#### 4.2.1 Static scratchpads

A static scratchpad memory is defined using a function SPM:  $\mathbb{M} \to \{true, false\}$ , which returns true for memory blocks that are stored in the scratchpad.

For an instruction scratchpad, each access to a memory block which is not stored in the scratchpad causes an additional bus access. Thus for each trace o, we have:

$$MEM_{sp}^{in}(o) = \left( \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (m^{in}, \_, \_) \wedge \neg SPM(m^{in}) \right\} \right|, \emptyset, \emptyset \right)$$

(6)

For a data scratchpad, we have to distinguish between a write-through (wt) policy, where each write-access results in a bus access:

$$\operatorname{MEM}_{\mathrm{sp-wt}}^{\mathrm{da}}(o) = \left( \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, r[m^{\mathrm{da}}]) \wedge \neg \operatorname{SPM}(m^{\mathrm{da}}) \right\} \right| + \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, w[m^{\mathrm{da}}]) \right\} \right|, \emptyset, \emptyset \right) \tag{7}$$

and a write-back (wb) policy, where each accessed memory block only results in one bus access at job completion, irrespective of the number of reads and writes to it:

$$\operatorname{MEM}_{\mathrm{sp-wb}}^{\mathrm{da}}(o) = \left( \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, r[m^{\mathrm{da}}]) \wedge \neg \operatorname{SPM}(m^{\mathrm{da}}) \right\} \right| + \left| \left\{ \iota_{i} | m^{\mathrm{da}} \in o \wedge \iota_{i} = (\_, \_, w[m^{\mathrm{da}}]) \right\} \right|, \emptyset, \emptyset \right).$$

(8)

As with other forms of local memory, the aim of a scratchpad is to reduce the number of bus accesses. An effective scratchpad configuration is obtained by storing the N most frequently used memory blocks, where N is the maximum number of memory blocks that the scratchpad can hold. With execution traces, identifying the most frequently used memory blocks is nearly trivial; however, in general more sophisticated optimization techniques have to be used (Falk and Kleinsorge 2009).

#### 4.2.2 Dynamic scratchpads

A scratchpad can be dynamic in two respects: (i) tasks can share the scratchpad space with other tasks, and (ii) a task can reload and change the scratchpad contents during its own execution. In the first case, the scratchpad configuration has to be loaded at the beginning of a task's execution and restored after each pre-emption. In the second case, different scratchpad contents are used for different sub-traces of the task. In the following, we only present the implementation of MEM for the first case, i.e., where the scratchpad is shared among different tasks. Extension to the second case is trivial.

In a slight abuse of notation, we model the pre-emption overhead in the case of shared scratchpads using sets of UCBs and ECBs. These are used to represent the memory blocks of a task that are stored in the scratchpad. A tighter integration, which

requires dedicated hardware support is described by Whitham et al. (2012, 2014); however, analysis for it is beyond the scope of this paper. As in the static case, a scratchpad memory is defined using a function SPM:  $\mathbb{M} \to \{true, false\}$ , which returns true for memory blocks that are stored in the scratchpad.

For an instruction scratchpad, for each trace o we define the set of memory blocks that are accessed by the trace and are stored in the scratchpad as follows:

$$\mathrm{ECB}_o^{\mathrm{in}} = \begin{cases} \left\{ m^{\mathrm{in}} | (m^{\mathrm{in}}, \_, \_) \in o \land \mathrm{SPM}(m^{\mathrm{in}}) \right\} & \mathrm{shared \ scratchpad} \\ \emptyset & \mathrm{dedicated \ scratchpad} \end{cases} \tag{9}$$

Similarly for a data scratchpad:

$$ECB_o^{da} = \begin{cases} \left\{ m^{da} | (\_, \_, r/w[m^{da}] \in o \land SPM(m^{da}) \right\} & \text{shared scratchpad} \\ \emptyset & \text{dedicated scratchpad} \end{cases}$$

(10)

The set of UCBs is then defined using the set of ECBs, i.e,  $\overline{\text{UCB}}_o^{\text{in/da}} = \{\text{ECB}_o^{\text{in/da}}\}$ In the case of an instruction scratchpad, each memory access to a memory block which is not stored in the scratchpad causes an additional bus access:

$$MEM_{sp}^{in}(o) = \left( \left| ECB_o^{in} \right| + \left| \left\{ \iota_i | \iota_i \in o \wedge \iota_i = (m^{in}, \_, \_) \wedge \neg SPM(m^{in}) \right\} \right|, \overline{UCB}_o^{in}, ECB_o^{in} \right)$$

(11)

The term  $|ECB_o^{in}|$  in (11) accounts for the initialization of the scratchpad at the start of the task in the case of a shared scratchpad. (The set  $ECB_o^{in}$  is empty in case of a dedicated scratchpad memory).

In the case of a data scratchpad, we again have to distinguish between a write-through (wt) policy and a write-back (wb) policy. Assuming a write-through policy, each write-access results in a bus access:

$$\operatorname{MEM}_{\mathrm{sp-wt}}^{\mathrm{da}}(o) = \left( \left| \operatorname{ECB}_{o}^{\mathrm{da}} \right| + \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, r[m^{\mathrm{da}}]) \wedge \neg \operatorname{SPM}(m^{\mathrm{da}}) \right\} \right| + \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, w[m^{\mathrm{da}}]) \right\} \right|, \overline{\operatorname{UCB}}_{o}^{\mathrm{da}}, \operatorname{ECB}_{o}^{\mathrm{da}} \right) \tag{12}$$

Whereas assuming a write-back policy, each memory block that is written to causes only one bus access at job completion:

$$\operatorname{MEM}_{\mathrm{sp-wb}}^{\mathrm{da}}(o) = \left( \left| \operatorname{ECB}_{o}^{\mathrm{da}} \right| + \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, r[m^{\mathrm{da}}]) \wedge \neg \operatorname{SPM}(m^{\mathrm{da}}) \right\} \right| + \left| \left\{ m^{\mathrm{da}} | (\_, \_, w[m^{\mathrm{da}}]) \in o \right\} \right|, \overline{\operatorname{UCB}}_{o}^{\mathrm{da}}, \operatorname{ECB}_{o}^{\mathrm{da}} \right). \tag{13}$$

#### 4.3 Caches

Caches are commonly used in multicore systems to bridge the performance gap between processor and main memory speeds. Unlike scratchpads they require no explicit management, rather the eviction of cache blocks is determined by the cache replacement policy. In this section, we consider both *cold* caches, representing the pessimistic case where the cache is empty or contains no useful blocks when a job of task starts to execute, and *warm* caches, where some useful blocks may persist from the execution of previous jobs of the same task.

#### 4.3.1 Cold caches

We assume a function Hit:  $\mathbb{I} \times \mathbb{M} \to \{true, false\}$ , which classifies each memory access at each instruction as a cache hit or a cache miss. This function can be derived using cache simulation of the access trace starting with an empty cache or by using traditional cache analysis (Ferdinand et al. 1999), where each unclassified memory access is considered a cache miss. This allows us to upper bound the number of cache misses. For each possible program point  $\iota$  on trace o (i.e. for each possible preemtion point), the set of UCBs is derived using the corresponding analysis described in the thesis of Altmeyer (2013, Chap. 5, Sect. 4): a forward cache analysis derives for each program point the set of cached memory blocks, and a backward cache analysis provides the set of memory blocks that will be reused before they may be evicted. The set of UCBs per program point  $\iota$  is then given by the intersection of the result of the forward and the backward cache analyses at  $\iota$ . For the purpose of our analysis, it is sufficient to store only the cache sets that useful memory blocks map to. The multiset  $UCB_o$  contains, for each program point  $\iota$  in trace o, the set of UCBs for that program point, i.e,  $\overline{\text{UCB}}_o = \bigcup_{\iota \in o} \{\text{UCB}_{\iota,o}\}$ . The set of ECBs is the set of cache sets that memory blocks accessed in trace o map to. Finally, the memory demand of trace o is given by the number of instructions in the trace that are not cache hits.

In the case of an instruction cache, we have:

$$MEM_{ca}^{in}(o) = \left( \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (m^{in}, \_, \_) \wedge \neg Hit(m^{in}, \iota_{i}) \right\} \right|, \overline{UCB}_{o}^{in}, ECB_{o}^{in} \right)$$

$$(14)$$

For a data cache, since we assume a write-through policy, each write access contributes a bus access, thus:

$$\operatorname{MEM}_{\operatorname{ca}}^{\operatorname{da}}(o) = \left( \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, r[m^{\operatorname{da}}]) \wedge \neg \operatorname{Hit}(m^{\operatorname{da}}, \iota_{i}) \right\} \right| + \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, w[m^{\operatorname{da}}]) \right\} \right|, \overline{\operatorname{UCB}}_{o}^{\operatorname{da}}, \operatorname{ECB}_{o}^{\operatorname{da}} \right) \tag{15}$$

#### 4.3.2 Warmed-up caches

Previously, we pessimistically assumed that each job of each task starts its execution with an empty cache. In reality, starting from the second job of a task, some of its instructions and data may still be cached when the job starts, reducing its execution time and memory demand. In order to capture this phenomenon, we propose an analysis that can be used to bound the response time of jobs after each task has run at least once, for example during a separate *start-up* phase.

We now consider which memory blocks can safely be assumed to be cached at the start of a job of task  $\tau_i$ , when another job of that task has run before. This set of memory blocks is determined by what *must* be cached at the end of the job's execution when it runs in isolation, minus those memory blocks that *may* be evicted by a job of any task  $\tau_j$  that can run *between* the two jobs of task  $\tau_i$ . Since task  $\tau_i$  is not active during this time, evicting jobs can belong to any task  $\tau_j$  with higher or lower priority than  $\tau_i$ .

Let, Cached(o) be the set of memory blocks that are cached after executing trace o of task  $\tau_i$  starting from an empty cache. For a given trace o, this set can be determined by simulation. The set of blocks that are definitely cached at the end of one run of the task in isolation is given by  $\bigcap_{o \in O_i} Cached(o)$ , where  $O_i$  is the set of traces representing the task. The set of memory blocks that are guaranteed to be cached after executing one job of a task could similarly be approximated by must-cache analysis (Ferdinand and Wilhelm 1999).

Let  $P_x$  be the core that task  $\tau_i$  executes on. The set of cache lines that may be evicted by tasks other than  $\tau_i$  is determined as follows:

$$POT-EVICTED_{i} = \bigcup_{\tau_{i} \in \Gamma_{x} \setminus \{\tau_{i}\}} \bigcup_{o \in O_{i}} ECB_{o}^{in} \cup ECB_{o}^{da}.$$

(16)

Given the sets defined above, we can compute the set of definitely cached memory blocks DEF-CACHED<sub>i</sub> of task  $\tau_i$  as follows:

$$DEF-CACHED_{i} = \left\{ b \in \bigcap_{o \in O_{i}} Cached(o) \middle| line(b) \notin POT-EVICTED_{i} \right\}, \quad (17)$$

where line(b) determines the cache line that memory block b maps to.

To take information about definitely cached memory blocks into account, we assume the function Hit from Sect. 4.3.1 is extended to take into account which blocks are guaranteed to be cached initially. The MEM functions for warmed-up instruction and data caches are hence:

$$\operatorname{MEM}_{\mathrm{ca,w}}^{\mathrm{in}}(o) = \left( \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (m^{\mathrm{in}}, \_, \_) \wedge \neg \operatorname{Hit}(m^{\mathrm{in}}, \iota_{i}, \operatorname{DEF-CACHED}_{i}) \right\} \right|, \\

\overline{\operatorname{UCB}}_{o}^{\mathrm{in}}, \operatorname{ECB}_{o}^{\mathrm{in}} \right) \tag{18}$$

$$\operatorname{MEM}_{\mathrm{ca,w}}^{\mathrm{da}}(o) = \left( \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, r[m^{\mathrm{da}}]) \wedge \neg \operatorname{Hit}(m^{\mathrm{da}}, \iota_{i}, \operatorname{DEF-CACHED}_{i}) \right\} \right| + \left| \left\{ \iota_{i} | \iota_{i} \in o \wedge \iota_{i} = (\_, \_, w[m^{\mathrm{da}}]) \right\} \right|, \overline{\operatorname{UCB}}_{o}^{\mathrm{da}}, \operatorname{ECB}_{o}^{\mathrm{da}} \right) \tag{19}$$

Note, in order to avoid any interference effects from the start-up or warm-up phase into regular operation, we assume the following protocol:

- 1. In the warm-up phase, a single job of each task is run non-preemptively on its allocated core. The order of task execution is arbitrary.

- 2. When the final job of the warm-up phase has finished, regular operation commences, and tasks are scheduled by fixed-priority preemptive scheduling.

Apart from the above protocol no further changes to the scheduling policy or analysis are needed to account for warmed-up caches.

#### 4.4 Memory combinations

To allow different combinations of local memories, for example scratchpad memory for instructions and an LRU cache for data, we define the combination of instruction memory MEM<sup>in</sup> and data memory MEM<sup>da</sup> as follows

$$\mathrm{MEM}(o) = \left(\mathrm{MD}_o^{\mathrm{in}} + \mathrm{MD}_o^{\mathrm{da}}, \overline{\mathrm{UCB}}_o^{\mathrm{in}} \cup \overline{\mathrm{UCB}}_o^{\mathrm{da}}, \mathrm{ECB}_o^{\mathrm{in}} \cup \mathrm{ECB}_o^{\mathrm{da}}\right) \tag{20}$$

with  $\operatorname{MEM^{in}}(o) = \left(\operatorname{MD_o^{in}}, \overline{\operatorname{UCB}_o^{in}}, \operatorname{ECB_o^{in}}\right)$  being the result for the instruction memory and  $\operatorname{MEM^{da}}(o) = \left(\operatorname{MD_o^{da}}, \overline{\operatorname{UCB}_o^{da}}, \operatorname{ECB_o^{da}}\right)$  the result for the data memory.

#### 5 Bus modelling

In this section we show how the memory bus delays experienced by a task can be modelled via a BUS function of the form:

BUS:

$$\mathbb{N} \times \mathbb{P} \times \mathbb{N} \to \mathbb{N}$$

(21)

where BUS(i, x, t) denotes an upper bound on the number of bus accesses that can delay completion of task  $\tau_i$  on core  $P_x$  during a time interval of length t. This abstraction covers a variety of bus arbitration policies, including Round-Robin, FIFO, Fixed-Priority, and Processor-Priority, all of which are *work-conserving*, and also TDMA which is not work-conserving.

We now introduce the mathematical representations of the delays incurred under these arbitration policies. We note that the framework is extensible to a wide variety of different policies. The only constraints we place on instantiations of the BUS(i, x, t) function is that they are monotonically non-decreasing in t.

Let  $\tau_i$  be the task of interest, and x the index of the core  $P_x$  on which it executes. Other task indices are represented by j, k etc. while y, z are used for core indices.

Let  $S_i^x(t)$  denote an upper bound on the total number of bus accesses due to  $\tau_i$  and all higher priority tasks that run on the same core  $P_x$  during an interval of length t, while one job of task  $\tau_i$  is active, i.e. within its response time. Let  $A_j^y(t)$  be an upper bound on the total number of bus accesses due to all tasks of priority j or higher executing on a different core  $P_y \neq P_x$  during an interval of length t. (Note, j may not necessarily be the priority of a task allocated to core  $P_y$ ). In Sect. 6.3 we show how the values of  $S_i^x(t)$ ,  $A_j^y(t)$  and  $L_j^y(t)$ , defined below, are computed and explain why  $S_i^x(t)$  and  $A_j^y(t)$  are subtly different and hence require distinct notation.

As memory bus requests are typically non-preemptive, one lower priority<sup>1</sup> memory request may block a higher priority one, since the global shared memory may have just received a lower priority request before the higher priority one arrives. To account for these blocking accesses, we use  $L_j^{\nu}(t)$  which denotes an upper bound on the total number of bus accesses due to all tasks of priority lower than j executing on some other core  $P_{\nu} \neq P_{x}$  during an interval of length t.

In the following equations for the BUS(i, x, t) function, we account for blocking due to one non-preemptive access from lower priority tasks running on the same core  $P_x$  as task  $\tau_i$  (this is the +1 in the equations). This holds because such blocking can only occur at the start of the priority level-i (processor) busy period.

For a fixed-priority bus with memory accesses inheriting the priority of the task that generates them, we have:

BUS

$$(i, x, t) = S_i^x(t) + \sum_{\forall y \neq x} A_i^y(t) + \min \left( S_i^x(t), \sum_{\forall y \neq x} L_i^y(t) \right) + 1$$

(22)

Here, the term  $S_i^x(t)$  covers the accesses from task  $\tau_i$  and higher priority tasks running on core  $P_x$ . The term  $\sum_{\forall y \neq x} A_i^y(t)$  is the interference due to accesses from higher priority tasks running on other cores. The term  $\min\left(S_i^x(t), \sum_{\forall y \neq x} L_i^y(t)\right)$  upper bounds the blocking due to tasks of lower priority than  $\tau_i$  running on other cores. (The number of blocking accesses is limited to one per access made by task  $\tau_i$  and higher priority tasks running on core  $P_x$  during time t i.e.  $S_i^x(t)$ , and also restricted to the maximum number of accesses made by tasks of lower priority than  $\tau_i$  running on other cores i.e.  $\sum_{y \neq x} L_i^y(t)$ ). Finally, the +1 accounts for a single blocking access from a task of priority lower than that of  $\tau_i$  on core  $P_x$ .

For a Processor-Priority bus with memory accesses inheriting the priority of the core rather than the task, we have:

BUS

$$(i, x, t) = S_i^x(t) + \sum_{y \in HP(x)} A_n^y(t) + \min \left( S_i^x(t), \sum_{y \in LP(x)} A_n^y(t) \right) + 1$$

(23)

<sup>&</sup>lt;sup>1</sup> Here we mean priorities on the bus, which are not necessarily the same as task priorities.

where HP(x) (LP(x)) is the set of cores with higher (lower) priority than that of  $P_x$ , and n is the index of the task with the lowest priority. The summation term  $\sum_{y \in HP(x)} A_n^y(t)$  captures the interference from all tasks (independent of their task priority) running on cores which have a higher processor priority than  $P_x$ . The term  $\min \left(S_i^x(t), \sum_{y \in LP(x)} A_n^y(t)\right)$  upper bounds the blocking due to tasks running on cores which have a processor priority lower than that of  $P_x$ .

A Round-Robin bus and a TDMA bus both make use of a pre-determined cycle of slots, where a slot is a time interval during which a single access can be serviced. Slots in the cycle are assigned to cores. With TDMA, the bus arbiter iterates over the cycle, taking the same time for each slot regardless of whether there is an access pending from the associated core, or not (i.e. the slot is empty). In contrast, a Round-Robin bus skips any empty slots, immediately moving to the next one with a pending access.

For a Round-Robin bus with v adjacent slots per core in a cycle of length  $\ell \cdot v$ , we have:

$$BUS(i, x, t) = S_i^x(t) + \sum_{\forall y \neq x} \min\left(A_n^y(t), v \cdot S_i^x(t)\right) + 1$$

(24)

The worst-case situation for each access in  $S_i^x(t)$  from core  $P_x$  occurs when it just misses its last slot in the cycle and is therefore delayed by v accesses by each core  $P_y \neq P_x$ . This leads to interference of at most  $v \cdot S_i^x(t)$  from each core  $P_y \neq P_x$ ; however, the overall interference from each core  $P_y$  is also bounded by the number of accesses  $A_n^y(t)$ , hence the min  $\left(A_n^y(t), v \cdot S_i^x(t)\right)$  term. Again, as we already account for all possible accesses from all other cores, there is no separate contribution to blocking.

For a TDMA bus with v adjacent slots per core in a cycle of length  $\ell \cdot v$ , we have:

$$BUS(i, x, t) = S_i^x(t) + ((\ell - 1) \cdot v) \cdot S_i^x(t) + 1$$

(25)

Since TDMA is not work-conserving, the worst case corresponds to each access in  $S_i^x(t)$  just missing the last slot in the cycle for core  $P_x$  and hence having to wait  $((\ell-1)\cdot v+1)$  slots to be serviced. Effectively, there is additional interference from the  $(\ell-1)\cdot v$  slots reserved for other cores on each access, irrespective of whether these slots are used or not (in contrast to Round-Robin). Note that when v=1, Eq. (25) simplifies to  $BUS(i,x,t)=\ell\cdot S_i^x(t)+1$ .

It is interesting to note that while TDMA provides more predictable behaviour, this is at a cost of significantly worse guaranteed performance over long time intervals (e.g. the response time of a task) due to the fact that it is not work-conserving. Effectively, this means that the memory accesses of a task may suffer additional interference due to empty slots on the bus. Nevertheless, Round-Robin behaves like TDMA when all other cores create a large number of competing memory accesses.

We note that the equal number of slots per core for Round-Robin and TDMA, and the grouping of slots per core are simplifying assumptions to exemplify how TDMA and Round-Robin buses can be analysed. An analysis for more complex configurations (patterns of slots) is reserved for future work.

For a FIFO bus, we assume that all accesses generated on the other cores may be serviced ahead of the last access of  $\tau_i$ , hence we have:

BUS

$$(i, x, t) = S_i^x(t) + \sum_{\forall y \neq x} A_n^y(t) + 1$$

(26)

Note that accesses from other cores do not contribute to blocking since we already pessimistically account for all these accesses in the summation term.

We note that the above analysis for a FIFO bus is potentially very pessimistic. If we assume that tasks busy wait on accesses and therefore only one access request per core can be in the FIFO queue at any given time then the worst-case situation for each access in  $S_i^x(t)$  from core  $P_x$  occurs when it finds the FIFO queue already contains one access request from each of the other cores. This case can be analysed using (24) for a Round-Robin bus assuming that v=1 i.e. one slot per core in the cycle. We note that some architectures may permit multiple requests to be queued by a single core (e.g. 8 in the case of the Kalray MPPA). Again, the bound on the number of requests in the queue means that the worst-case analysis equates to that for a Round-Robin bus assuming that v=8 i.e. 8 slots per core in the cycle. We include pure FIFO behaviour here to illustrate the degraded performance in this case.

#### 6 Response time analysis

In this section, we present the nucleus of our timing verification framework: interference-aware MRTA. This analysis integrates the processor and memory demands of the task of interest and higher priority tasks running on the same core, including CRPD. It also accounts for the cross-core interference on the memory bus due to tasks running on the other cores.

A task set is deemed schedulable, if for each task  $\tau_i$ , its response time  $R_i$  is less than or equal to its deadline  $D_i$ :

$$\forall_i : R_i < D_i \Rightarrow \text{ schedulable}$$

The traditional response time calculation (Audsley et al. 1993; Joseph and Pandya 1986) for fixed-priority pre-emptive scheduling on a uniprocessor is based on an upper bound on the WCET of each task  $\tau_i$ , denoted by  $C_i$ . By contrast, our MRTA framework dissects the individual components (processor and memory demands) that contribute to the WCET bound and re-assembles them at the level of the worst-case response time. It thus avoids the over-approximation inherent in using context-independent WCET bounds.

In the following, we assume that  $\tau_i$  is the task of interest whose schedulability we are checking, and  $P_x$  is the core on which it runs. Recall that there is a unique global ordering of task priorities even though the scheduling is partitioned with a fixed-priority pre-emptive scheduler on each core.

#### 6.1 Interference on the core

We compute the maximal processor demand PD<sub>i</sub> for each task  $\tau_i$  as follows:

$$PD_{i} = \max_{o \in O_{i}} \sum_{(\Delta, \Delta, b) \in o} \Delta$$

(27)

where  $\Delta$  is the execution time of an instruction without memory delays. Task  $\tau_i$  suffers interference  $I^{\text{PROC}}(i, x, t)$  on its core  $P_x$  due to tasks of higher priority running on the same core within a time interval of length t starting from the critical instant:

$$I^{\text{PROC}}(i, x, t) = \sum_{j \in \Gamma_X \land j \in \text{hp}(i)} \left\lceil \frac{t}{T_j} \right\rceil \text{PD}_j$$

(28)

#### 6.2 Interference on the local memory

Local memory improves a task's execution time by reducing the number of accesses to main memory. The memory demand of a trace gives the number of accesses that go to main memory and hence the bus, despite the presence of the local memory. The maximal memory demand  $MD_i$  of a task  $\tau_i$  is defined by the maximum number of bus accesses of any of its traces:

$$MD_{i} = \max_{o \in O_{i}} \left\{ MD \middle| MEM(o) = (MD, \_, \_) \right\}$$

(29)

Note that the maximal memory demand refers to the demand of the combined instruction and data memory as defined in Eq. (20).

The memory demand  $\mathrm{MD}_i$  is derived assuming non-preemptive execution, i.e. that the task runs to completion without interference on the local memory. The sets of UCBs and ECBs are used to compute the additional overhead due to pre-emption. In the computation of this overhead, we use the sets of UCBs per trace o to preserve precision,

$$\overline{\text{UCB}}_o = \overline{\text{UCB}} \text{ with } \text{MEM}(o) = (\_, \overline{\text{UCB}}, \_)$$

(30)

and derive the maximal set of ECBs per task  $\tau_i$  as the union of the ECBs on all traces.

$$ECB_i = \bigcup_{o \in O_i} \left\{ ECB \middle| MEM(o) = (\_, \_, ECB) \right\}$$

(31)

We use  $\gamma_{i,j,x}$  (with  $j \in \text{hp}(i)$ ) to denote the overhead (additional accesses) due to a pre-emption of task  $\tau_i$  by task  $\tau_j$  on core  $P_x$ .

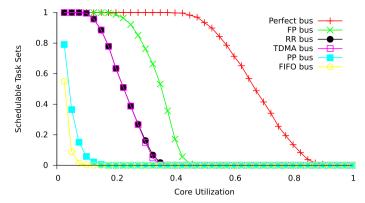

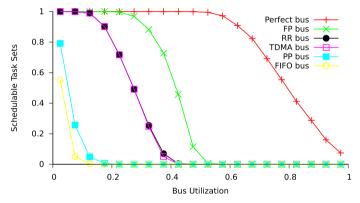

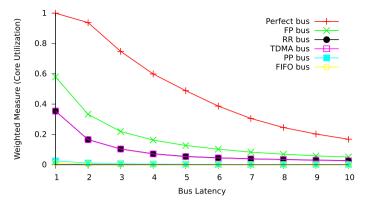

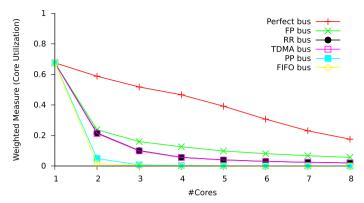

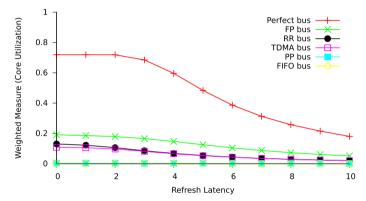

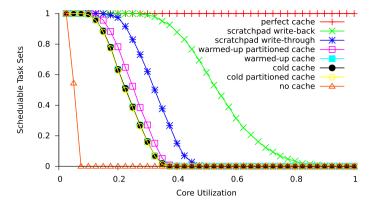

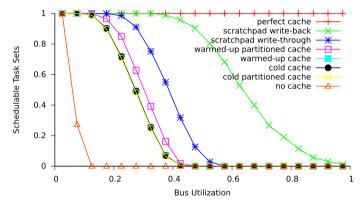

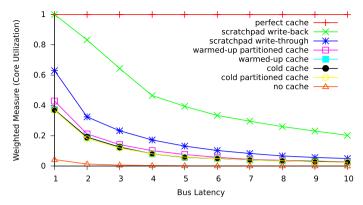

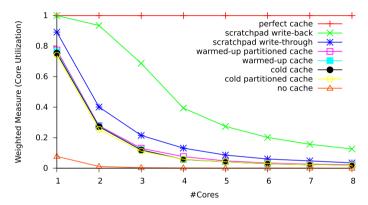

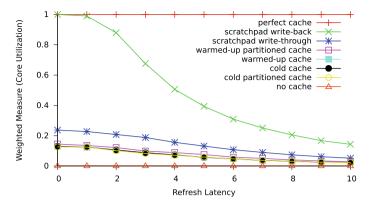

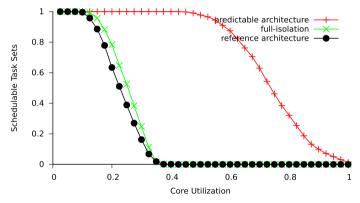

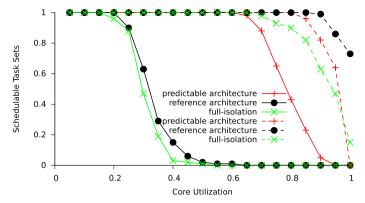

We use the ECB-Union (Altmeyer et al. 2011, 2012) approach as an exemplar of CRPD analysis, as it provides a reasonably precise bound on the pre-emption overhead with low complexity. (Other CRPD analysis techniques (Altmeyer et al. 2012; Lee et al. 2001) could also be integrated into this framework). The ECB-Union