# PhD Thesis

Integrating dataflow and non-dataflow realtime application models on multi-core platforms

### **Hazem Ali**

CISTER-TR-170512

2017/05/23

# Integrating dataflow and non-dataflow real-time application models on multi-core platforms

### Hazem Ali

\*CISTER Research Centre

Polytechnic Institute of Porto (ISEP-IPP)

Rua Dr. António Bernardino de Almeida, 431

4200-072 Porto

Portugal

Tel.: +351.22.8340509, Fax: +351.22.8321159

E-mail: haali@isep.ipp.pt http://www.cister.isep.ipp.pt

### **Abstract**

# Integrating Dataflow and Non-Dataflow Real-time Application Models on Multi-core Platforms

Hazem Ismail Abdelaziz Ali

Programa Doutoral em Engenharia Eletrotécnica e de Computadores

Supervisor: Prof. Dr. Luís Miguel Rosário da Silva Pinho

Co-Supervisor: Dr. Kjell Benny Åkesson

## Integrating Dataflow and Non-Dataflow Real-time Application Models on Multi-core Platforms

### Hazem Ismail Abdelaziz Ali

Programa Doutoral em Engenharia Eletrotécnica e de Computadores

## Approved by:

**President** : Dr. José Alfredo Ribeiro da Silva Matos

**External Referee**: Dr. Sander Stuijk **External Referee**: Dr. Johan Eker

Internal Referee : Dr. Luís Miguel Pinho de AlmeidaInternal Referee : Dr. Mário Jorge Rodrigues de Sousa

**Supervisor** : Dr. Luís Miguel Rosário da Silva Pinho

## **Abstract**

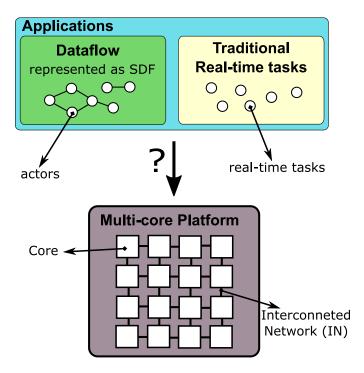

Day by day, gradually and steadily, applications in all segments of computing, including embedded systems, are getting more complex, because of the increased range of functionality they offer. This complexity requires platforms with increased performance that satisfies such growing computational demands. This need has driven the adoption of multi-core processors in embedded systems, since they allow performance to be increased at a reasonable energy consumption.

Future real-time embedded systems will increasingly incorporate mixed application models with timing constraints running on the same multi-core platform. These application models are dataflow applications with timing constraints and traditional real-time applications modelled as independent arbitrary-deadline tasks. Examples of such mixed embedded systems are Autonomous Driving Systems and Unmanned Ariel Vehicles. These systems require guarantees that all running applications execute satisfying their timing constraints. Also, to be cost-efficient in terms of design, they require efficient mapping strategies that maximize the use of system resources to reduce the overall cost.

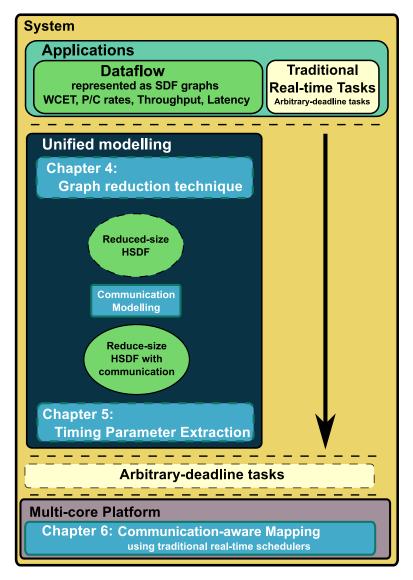

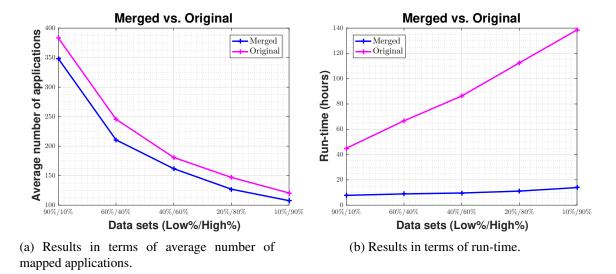

This work proposes a complete approach with a main goal to integrate mixed application models (dataflow and traditional real-time applications) with timing requirements on the same multi-core platform. This approach guarantees that the mapped applications satisfy their timing constraints and maximize utilization of the platform resources. Three main algorithms to achieve the main goal. The first algorithm is called *slack-based merging*, which is an offline dataflow graph reduction technique that aims to decrease the complexity of dataflow applications, and thereby their analysis time. The algorithm reduces the run-time of our approach with 82% to 90%, compared to when it is not used. The experimental evaluation with real application models from the SDF<sup>3</sup> benchmark shows that the reduced graph: 1) respects the timing constraints, i.e. *throughput* and *latency*, of the original application graph and 2) when the throughput constraint is relaxed with respect to the maximal throughput of the graph, the merging algorithm is able to achieve a larger reduction in graph size.

The second algorithm is called *Timing Parameter Extraction*, which extracts timing parameters, i.e. *offsets*, *periods* and *deadlines*, of dataflow applications with timing constraints, i.e. *throughput* and *latency*, converting them into periodic arbitrary-deadline tasks. These tasks execute in a way that preserve the dependencies of the original dataflow application using the *offset* parameter, while satisfying its timing constraints using the *period* and *deadline* parameters. This algorithm is a means to *unify the two mixed application models* into a single real-time task set. The main advantage of this algorithm is that the extraction of the timing parameters is independent of the specific scheduler being used, of other applications running in the system and the details of the particular platform. In addition, the experimental evaluation shows that the reduced-size dataflow graphs generated by the *slack-based merging* algorithm, in particular for applications that do not need to execute at maximum throughput, help speeding up the extraction of the timing parameters.

The third algorithm is called *communication-aware mapping*, which allocates the mixed application models on a 2D-Mesh multi-core platform after unifying them. The mapping process is

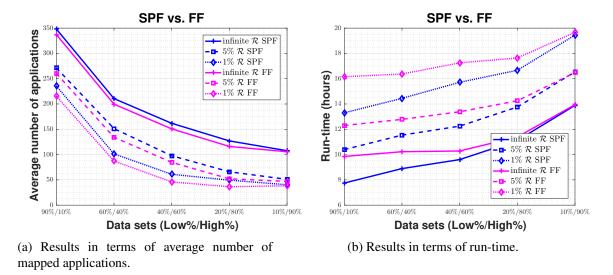

done considering the timing constraints of the applications and maximizing resource utilization of the platform, while accounting for the communication cost of the dataflow applications. The algorithm is based on a novel mapping heuristic called *Sensitive-Path-First*, which surpasses the well-known First Fit bin-packing heuristic in terms of number of allocated applications and runtime by up to 28% and 22%, respectively. The experimental evaluation reveals a direct relation between the number of allocated applications and the availability of communication resources, which demonstrates the importance of considering communication cost. We also show that ignoring communication cost, as frequently done in existing work, allows 76% more applications to be mapped, although the applications in the system are no longer guaranteed to satisfy their timing constraints.

Together, these three important algorithms successfully achieve the main goal of this thesis and play a part in allowing embedded real-time systems to map and schedule mixed application models. The complete approach and the three algorithms presented in this thesis have been validated through proofs and experimental evaluation.

## Resumo

À semelhança do que acontece noutros domínios da computação, os sistemas embebidos estão cada vez mais complexos, devido ao aumento e diversidade das funcionalidades que fornecem, o que tem levado à necessidade de plataformas com maior desempenho. Esta exigência tem levado à cada vez maior adoção de plataformas multi-núcleo de processamento (*multi-core*) neste tipo de sistemas, permitindo o aumento de desempenho com custos razoáveis de energia.

Os sistemas embebidos do futuro integrarão na mesma plataforma multi-núcleo aplicações com diferentes modelos de computação, e com requisitos temporais. Entre estas é expectável a necessidade de integrar aplicações tradicionais de tempo-real (modelizadas por tarefas independentes) com aplicações modelizadas por fluxos de dados (*dataflow*). Exemplos podem ser encontrados em sistemas de condução autónoma ou veículos aéreos sem piloto, sistemas que requerem a garantia de cumprimentos dos prazos temporais de todas as aplicações. Para além disso, são sistemas em que é fundamental a existência de estratégias automatizadas de mapeamento da computação que maximizem a utilização dos recursos disponibilizados pela plataforma.

Esta dissertação propõe uma metodologia completa para a integração numa só plataforma multi-núcleo de aplicações com modelos computacionais distintos (fluxo de dados e tradicionais tempo-real) e com requisitos temporais. Esta metodologia permite garantir que as aplicações cumprem com os seus requisitos temporais, ao mesmo tempo que maximiza a utilização dos recursos do sistema. Para este efeito, a metodologia inclui três algoritmos diferentes.

Num primeiro passo, é utilizado um algoritmo, *slack-based merging*, para reduzir a complexidade dos grafos de fluxo de dados com que são modelizadas as aplicações que utilizam este modelo computacional, o que permite reduzir o tempo de análise das mesmas. Este algoritmo permite reduzir o tempo de processamento do processo de 82% a 90%. A avaliação experimental com modelos de aplicações reais, do benchmark SDF<sup>3</sup> demonstra que o grafo reduzido: 1) respeita os requisites temporais do grafo original, i.e., o desempenho (*throughput*) e a latência (*latency*), e 2) quando se relaxa o requisito de desempenho em relação ao máximo permitido pelo grafo, o algoritmo permite uma maior redução do tamanho do grafo.

O segundo algoritmo, *Timing Parameter Extraction*, permite extrair as características temporais tradicionais de uma aplicação de tempo-real, i.e., períodos (*periods*), prazos (*deadlines*) e deslocamentos (*offsets*), a partir dos modelos de fluxo de dados com requisitos de desempenho (*throughput*) e latência (*latency*), convertendo assim estes fluxos em tarefas periódicas independentes. Estas tarefas executam de forma a preservar as dependências do modelo de fluxo de dados original através do deslocamento da ativação de tarefas consequentes, satisfazendo os requisitos de processamento e latência através dos períodos de ativação e prazos temporais. Este algoritmo permite assim unificar os dois modelos distintos de computação, num só conjunto de tarefas de tempo-real. A vantagem principal deste algoritmo é que esta extração de parâmetros é independente do escalonador utilizado, de outras aplicações que executam no sistema, e dos detalhes da plataforma. A avaliação experimental também demonstra que o tempo de processamento desta extração é reduzido pela redução dos grafos obtida pelo algoritmo anterior, particularmente para

aplicações que não necessitam executar com o máximo desempenho.

O terceiro algoritmo, *communication-aware mapping*, mapeia as tarefas das aplicações que usam os dois modelos de computação, após unificação, em plataforma multi-núcleo com comunicação em 2 dimensões entre núcleos (2D-Mesh). O mapeamento é efetuado considerando os requisites temporais das aplicações, e maximiza a utilização dos recursos computacionais da plataforma, tendo em consideração os potenciais custos de comunicação. Este algoritmo é baseado numa noval heurística, *Sensitive-Path-First*, a qual obtém melhores resultados que a heurística *First-Fit*, tanto em termos de número de aplicações mapeadas como em tempo de processamento (28% e 22% melhor, respetivamente). A avaliação experimental mostra uma relação direta entre o número de aplicações mapeadas e a disponibilizada de recursos de Comunicação, o que demonstra a importância da consideração destes custos durante o mapeamento. Também mostramos que, ignorando os custos de comunicação, como é habitualmente feito em trabalhos semelhantes, permite mapear até 76% mais aplicações, embora sem conseguir garantir a satisfação dos seus requisitos temporais.

Em conjunto, estes três algoritmos importantes permitem atingir com sucesso o objetivo principal desta dissertação, potenciando o mapeamento e integração em sistemas embebidos de temporeal de aplicações com modelos computacionais distintos. A metodologia complete e os três algoritmos apresentados na dissertação foram validados por provas e avaliação experimental.

# Acknowledgements

Undertaking this PhD has been a truly life-changing experience. Like most research work, this PhD is the result of a curious and inquisitive spirit, coupled with plenty of hard work and persistence. Naturally, it was difficult at times, but overall, the fulfilling moments far exceeded the hardship ones. This research would not be possible to do it without the support and guidance that I received from a lot of people, to whom I will always be grateful.

First, I would like to express my sincere gratitude to my supervisor Prof. Luís Miguel Pinho for believing in me and giving me the chance to work with him. His continuous guidance, patience, motivation, and support through my entire PhD studies helped me in all time of research. Also, I wish to extend a sincere and heartfelt thanks to my co-supervisor Dr. Benny Akesson on both professional and personal level. On professional level, for his dedication and comprehensive assistance through my entire research journey. His sharp insights, valuable feedback and detailed discussions with him, helped in shaping up my research till this final outcome. On the personal level, Benny is one of the friendliest persons that you forget that he is actually your supervisor. He always maintains a personal relation with his students where he socialize and involve in different activities. I will never forget our interesting long runs, where we had fun and enjoyable discussions.

Second, a huge thank goes to Dr. Stefan Markus Petters. Although we did not work directly together, he was one of the main reasons to join CISTER research group. He was kind enough to listen to my counter argument, after he sent an email not accepting me for the PhD position. This normally does not happen in applying for PhD positions. I am really grateful for him.

Third and most important, none of this achievements would have been possible without the love and patience of my family. My parents, Ismail Abdelaziz Ali and Somaia Mohamed Elsayad, have been a constant source of love, concern, support and strength all these years. Especially my mother, Somaia Mohamed Elsayad, for the long hours she invested teaching me mathematics, algerbra and geometry that made me like engineering. I owe her what I am right now. Also, I would like to express my heartfelt gratitude to my brothers and sister, Mohamed Abdelaziz, Ahmed and Reham, for their continuous encouragement during my long research journey that started in 2008, going to sweden for doing my masters degree.

Fourth, my dear friend and CISTER companion Borislav Nikolić. We have spent more than six years together at CISTER, where we shared a very memorable moments of happiness, success and lifetime achievements. His valuable advice along with his cheerful and funny spirit made my PhD life easier. I deeply thank him very much. I will never forget such times and I wish you all the best in your life and career.

Fifth, Prof. Eduardo Tovar for creating an outstanding work environment in CISTER Research Center. I have always enjoyed the working environment in our office, with great office mates. Especially Muhammad Ali Awan and Claudio Maia for being good friends and colleagues. During these six years, we have had all the interesting discussions covering a variety of topics, such as technology, sports, culture etc. I would like to add that I feel fortunate to have known

Ricardo Garibay, Hossein Fotouhi, Maryam Vahabi, Artem Burmyakov, Kostiantyn Berezovskyi, Gurulingesh Raravi, Dakshina Dasari, António Barros, Paulo Baltarejo, Syed Aftab Rashid and Harrison Kurunathan during these years. Last but not the least, I extend my gratitude to all the staff members at CISTER Research Center, who have made these years more enjoyable.

This work was partially supported by FCT (Fundação para a Ciência e Tecnologia) under the individual doctoral grant SFRH/BD/79872/2011.

Hazem Ismail Ali

# **List of Publications**

#### **Articles Included in this Thesis**

- Hazem Ismail Ali, Luís Miguel Pinho and Benny Akesson, "Critical-Path-First based allocation of real-time streaming applications on 2D mesh-type multi-cores," in IEEE 19th International Conference on Embedded and Real-Time Computing Systems and Applications, Taipei, 2013, pp. 201-208. doi: 10.1109/RTCSA.2013.6732220, URL: http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6732220&isnumber=6732192

- <u>Hazem Ismail Ali</u>, Benny Akesson and Luís Miguel Pinho, "Generalized Extraction of Real-Time Parameters for Homogeneous Synchronous Dataflow Graphs," in **23rd Euromicro International Conference on Parallel, Distributed, and Network-Based Processing, Turku, 2015**, pp. 701-710. doi: 10.1109/PDP.2015.57, URL:

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=7092796&isnumber=7092002

- <u>Hazem Ismail Ali</u>, Sander Stuijk, Benny Akesson, and Luís Miguel Pinho. "*Reducing the complexity of dataflow graphs using slack-based merging*,". in **ACM Transactions on Design Automation of Electronic Systems**, 22, 2, Article 24 (January 2017), 22 pages. ISSN 1084-4309. doi: 10.1145/2956232. URL: http://dx.doi.org/10.1145/2956232

- <u>Hazem Ismail Ali</u>, Benny Akesson and Luís Miguel Pinho. *Combining dataflow applications and real-time task sets on multi-core platforms*. In **Proceedings of the 20th International Workshop on Software and Compilers for Embedded Systems** (SCOPES '17), Sander Stuijk (Ed.). ACM, New York, NY, USA, 60-63. doi: 10.1145/3078659.3078671 URL: https://doi.org/10.1145/3078659.3078671

### Other Articles

- <u>Hazem Ismail Ali</u> and Luís Miguel Pinho. 2011. "A parallel programming model for ada". In Proceedings of the 2011 ACM annual international conference on Special interest group on the ada programming language (SIGAda '11). ACM, New York, NY, USA, 19-26. DOI=http://dx.doi.org/10.1145/2070337.2070350

- Borislav Nikolić, <u>Hazem Ismail Ali</u>, Stefan M. Petters, and Luís Miguel Pinho. 2013. "Are virtual channels the bottleneck of priority-aware wormhole-switched NoC-based many-cores?". In Proceedings of the 21st International conference on Real-Time Networks and Systems (RTNS '13)". ACM, New York, NY, USA, 13-22. DOI=http://dx.doi.org/10.1145/2516821.2516845

| But even if y | "Science is not going to yield anything ou do devote yourself entirely, it remains | g unless you devote yourself completely<br>uncertain whether you will get anything<br>from it." |

|---------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|               |                                                                                    | Ibrahim Al-Nazzam                                                                               |

|               |                                                                                    |                                                                                                 |

|               |                                                                                    |                                                                                                 |

|               |                                                                                    |                                                                                                 |

|               |                                                                                    |                                                                                                 |

# **Contents**

| List of Abbreviations xx |         |                                           | XXi   |

|--------------------------|---------|-------------------------------------------|-------|

| Li                       | st of S | Symbols                                   | xxiii |

| 1                        | Intr    | oduction                                  | 1     |

|                          | 1.1     | Real-time Computational Model             | 2     |

|                          |         | 1.1.1 Real-time Applications              | 3     |

|                          |         | 1.1.2 Worst-Case Execution Time           | 4     |

|                          | 1.2     | Dataflow Computational Model              | 5     |

|                          |         | 1.2.1 Dataflow Applications               | 5     |

|                          |         | 1.2.2 Streaming Applications              | 7     |

|                          | 1.3     | Processing Platform                       | 8     |

|                          | 1.4     | Problem Statement                         | 12    |

|                          | 1.5     | Solution Overview                         | 13    |

|                          | 1.6     | Thesis Contributions                      | 15    |

|                          | 1.7     | Thesis Organization                       | 16    |

| 2                        | State   | e of the Art                              | 19    |

|                          | 2.1     | Dataflow Graph Analysis                   | 19    |

|                          | 2.2     | Timing Parameter Extraction               | 21    |

|                          | 2.3     | Efficient Mapping                         | 23    |

| 3                        | Bacl    | kground                                   | 27    |

|                          | 3.1     | Real-time Systems                         | 27    |

|                          |         | 3.1.1 Multi-core Scheduling               | 29    |

|                          |         | 3.1.2 Feasibility Tests                   | 29    |

|                          | 3.2     | Dataflow Computational Model              | 32    |

|                          |         | 3.2.1 Synchronous Dataflow                | 32    |

|                          |         | 3.2.2 Homogenous Synchronous Dataflow     | 34    |

|                          |         | 3.2.3 Buffer Modelling in Dataflow Graphs | 35    |

|                          | 3.3     | Multi-/Many-Core Platforms                | 35    |

|                          | 3.4     | System Model                              | 39    |

| 4                        | Red     | ucing Complexity of Dataflow Graphs       | 41    |

|                          | 4.1     | Definitions                               | 42    |

|                          | 4.2     | Safe Merge                                | 44    |

|                          |         | 4.2.1 Definition and Function             | 44    |

|                          |         | 4.2.2 A Safe Merge is Deadlock-Free       | 45    |

|                          | 4.3     | Slack-Based Merging Algorithm             | 47    |

xii CONTENTS

|   |     | 4.3.1 Merging Strategy                  | y                                 | <br> | <br> | <br>47 |

|---|-----|-----------------------------------------|-----------------------------------|------|------|--------|

|   |     | 4.3.2 Valid Merge                       |                                   | <br> | <br> | <br>48 |

|   |     | 4.3.3 The Algorithm                     |                                   | <br> | <br> | <br>49 |

|   |     | 4.3.4 Complexity Ana                    | ılysis                            | <br> | <br> | <br>51 |

|   |     | 4.3.5 Example                           |                                   | <br> | <br> | <br>51 |

|   | 4.4 | Experiments                             |                                   | <br> | <br> | <br>52 |

|   | 4.5 | Summary                                 |                                   | <br> | <br> | <br>54 |

| 5 | Tim | ing Parameter Extractio                 | on .                              |      |      | 55     |

|   | 5.1 | Preliminaries                           |                                   | <br> | <br> | <br>55 |

|   | 5.2 |                                         | rategies for Pipelines            |      |      | 56     |

|   |     | _                                       | thod                              |      |      | 56     |

|   |     | 5.2.2 The PURE Meth                     | nod                               | <br> | <br> | <br>57 |

|   | 5.3 |                                         |                                   |      |      | 57     |

|   | 5.4 | Deriving Latency Constr                 | raints                            | <br> | <br> | <br>58 |

|   |     | - · · · · · · · · · · · · · · · · · · · | aints for Cyclic Paths            |      |      | 59     |

|   |     | 5.4.2 Deriving End-to-                  | -End Latency Constraint           | <br> | <br> | <br>59 |

|   | 5.5 | Timing Parameters Extra                 | action Algorithm                  | <br> | <br> | <br>60 |

|   |     |                                         | ling All Time-Constrained Paths . |      |      | 60     |

|   |     | 5.5.2 Second phase: E                   | Extracting Timing Parameters      | <br> | <br> | <br>62 |

|   |     | 5.5.3 Complexity Ana                    | ılysis                            | <br> | <br> | <br>64 |

|   |     | 5.5.4 Example                           |                                   | <br> | <br> | <br>65 |

|   | 5.6 | Validation of the TPE alg               | gorithm                           | <br> | <br> | <br>66 |

|   | 5.7 | Experiments                             |                                   | <br> | <br> | <br>69 |

|   |     | 5.7.1 Experimental Se                   | etup                              | <br> | <br> | <br>70 |

|   |     | 5.7.2 Experimental Re                   | esults                            | <br> | <br> | <br>71 |

|   | 5.8 | Summary                                 |                                   | <br> | <br> | <br>74 |

| 6 | Con | nmunication-Aware Map                   | pping                             |      |      | 75     |

|   | 6.1 | -                                       | ion Cost                          | <br> | <br> | <br>76 |

|   | 6.2 | · ·                                     | logy                              |      |      | 79     |

|   | 6.3 |                                         | Mapping                           |      |      | 80     |

|   |     |                                         | nality                            |      |      | 82     |

|   |     |                                         | irst Algorithm                    |      |      | 83     |

|   | 6.4 | Limitations                             |                                   | <br> | <br> | <br>85 |

|   | 6.5 | Complexity Analysis .                   |                                   | <br> | <br> | <br>86 |

|   |     |                                         | -Aware Mapping                    |      |      | 86     |

|   |     | 6.5.2 Complete Appro                    | oach                              | <br> | <br> | <br>87 |

|   | 6.6 |                                         |                                   |      |      | 87     |

|   |     | 6.6.1 General Experim                   | nental Setup                      | <br> | <br> | <br>87 |

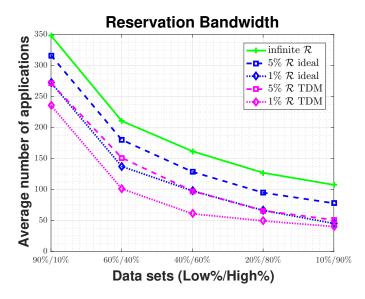

|   |     | _                                       | e Communication Cost              |      |      | 88     |

|   |     | 6.6.3 Evaluation of the                 | e Mapping Heuristic               | <br> | <br> | <br>90 |

|   |     | 6.6.4 Evaluation of Sla                 | ack-based Merging                 | <br> | <br> | <br>91 |

|   | 6.7 | Summary                                 |                                   | <br> | <br> | <br>93 |

| Co  | nclusion | and Future Directions             |

|-----|----------|-----------------------------------|

| 7.1 | Conclu   | usions                            |

|     | 7.1.1    | Slack-Based Merging               |

|     | 7.1.2    | Timing Parameter Extraction       |

|     | 7.1.3    | Communication-Aware Mapping       |

| 7.2 | Future   | Work                              |

|     | 7.2.1    | Timing Parameter Extraction (TPE) |

|     | 7.2.2    | Communication-Aware Mapping       |

xiv CONTENTS

# **List of Figures**

| 1.1 | Dataflow application                                                                                      |

|-----|-----------------------------------------------------------------------------------------------------------|

|     | 1.1(a)                                                                                                    |

|     | 1.1(b)                                                                                                    |

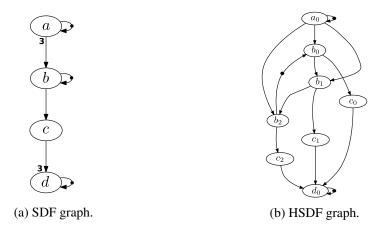

| 1.2 | Example of SDF and HSDF graphs                                                                            |

|     | 1.2(a) SDF graph                                                                                          |

|     | 1.2(b) HSDF graph                                                                                         |

| 1.3 | Examples of embedded systems running streaming applications                                               |

|     | 1.3(a) Smartphones [Kenya Tech News, 2015]                                                                |

|     | 1.3(b) Autonomous driving systems [Daily Autonomous Car News, 2015] 8                                     |

| 1.4 | Examples of Interconnection Networks (IN) [Sanchez et al., 2010]                                          |

|     | 1.4(a) 2D Mesh                                                                                            |

|     | 1.4(b) Fat Tree                                                                                           |

|     | 1.4(c) Flattened Butterfly                                                                                |

| 1.5 | Problem to be addressed                                                                                   |

| 1.6 | Solution outline                                                                                          |

|     |                                                                                                           |

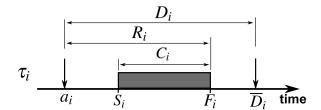

| 3.1 | Real-time task parameters                                                                                 |

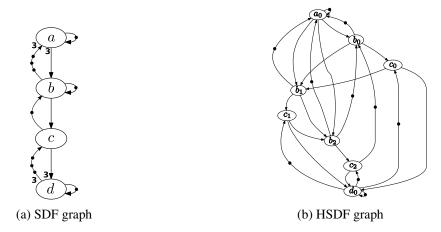

| 3.2 | An SDF graph and its HSDF representation                                                                  |

|     | 3.2(a) SDF graph                                                                                          |

|     | 3.2(b) HSDF graph                                                                                         |

| 3.3 | An SDF graph and its HSDF representation with finite-size buffers                                         |

|     | 3.3(a) SDF graph                                                                                          |

|     | 3.3(b) HSDF graph                                                                                         |

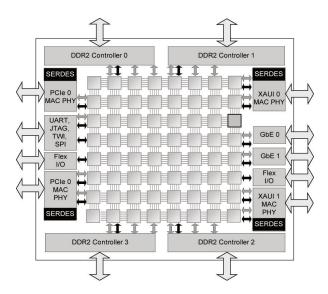

| 3.4 | TILE64 <sup>TM</sup> block diagram [Bell et al., 2008]                                                    |

| 3.5 | A TDM frame with frame size $\mathcal{F}$ of 6 where 2 allocated slots $\varkappa_1$ to application $A_1$ |

|     | for continous slot assignment policy [Akesson et al., 2015]                                               |

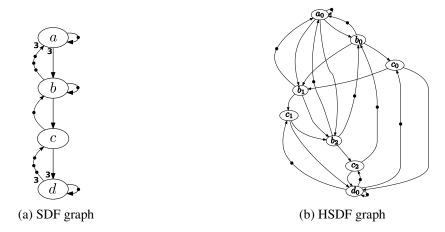

| 4.1 | An SDF graph and its HSDF representation                                                                  |

|     | 4.1(a) SDF graph                                                                                          |

|     | 4.1(b) HSDF graph                                                                                         |

| 4.2 | An SDF graph and its HSDF representation with finite-size buffers                                         |

|     | 4.2(a) SDF graph                                                                                          |

|     | 4.2(b) HSDF graph                                                                                         |

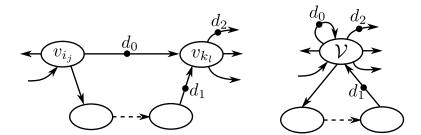

| 4.3 | A safe merge operation of two independent firings $(v_{i_1}, v_{k_l})$ into a new cluster $\mathcal{V}$ . |

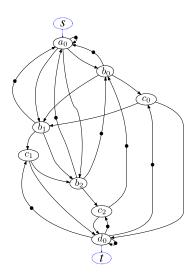

| 4.4 | HSDF graph after adding $s$ and $t$                                                                       |

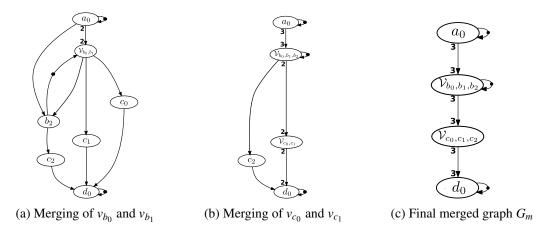

| 4.5 | Example of slack-based merging                                                                            |

|     | 4.5(a) Merging of $v_{b_0}$ and $v_{b_1}$                                                                 |

|     | 4.5(b) Merging of $v_{c_0}$ and $v_{c_1}$                                                                 |

xvi LIST OF FIGURES

|                 | 4.5(c) Final merged graph $G_m$                                                     |

|-----------------|-------------------------------------------------------------------------------------|

| 5.1             | HSDF graph after adding source $s$ and sink $t$                                     |

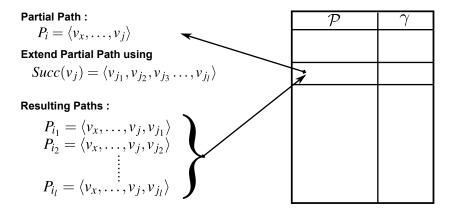

| 5.2             | Enumeration of time-constrained paths                                               |

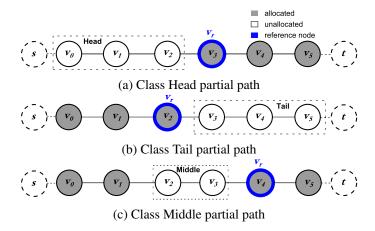

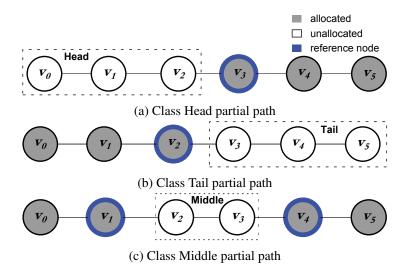

| 5.3             | Partial path classes for offsets setting                                            |

|                 | 5.3(a) Class Head partial path                                                      |

|                 | 5.3(b) Class Tail partial path                                                      |

|                 | 5.3(c) Class Middle partial path                                                    |

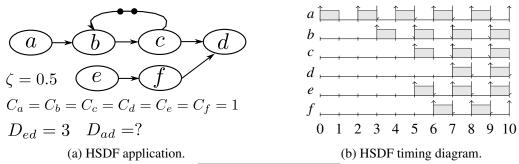

| 5.4             | HSDF example                                                                        |

| J. <del>T</del> | 5.4(a) HSDF application                                                             |

|                 | 5.4(b) HSDF timing diagram                                                          |

|                 | 5.4(c) Actors' timing parameters                                                    |

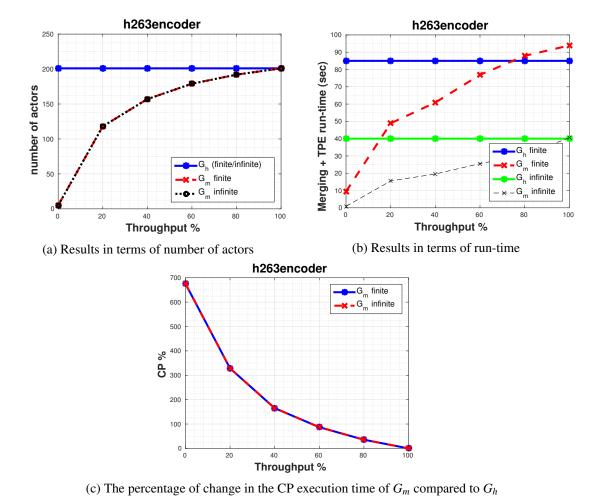

| 5.5             | <i>h263encoder</i> results                                                          |

| 5.5             | 5.5(a) Results in terms of number of actors                                         |

|                 | 5.5(b) Results in terms of run-time                                                 |

|                 | 5.5(c) The percentage of change in the CP execution time of $G_m$ compared to $G_h$ |

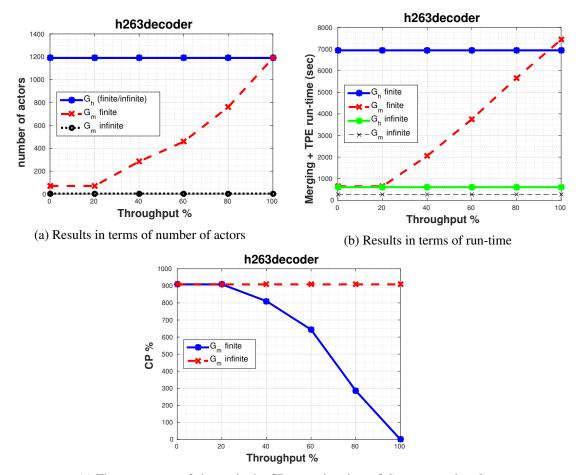

| 5.6             |                                                                                     |

| 3.0             | <i>h263decoder</i> results                                                          |

|                 |                                                                                     |

|                 |                                                                                     |

|                 | 5.6(c) The percentage of change in the CP execution time of $G_m$ compared to $G_h$ |

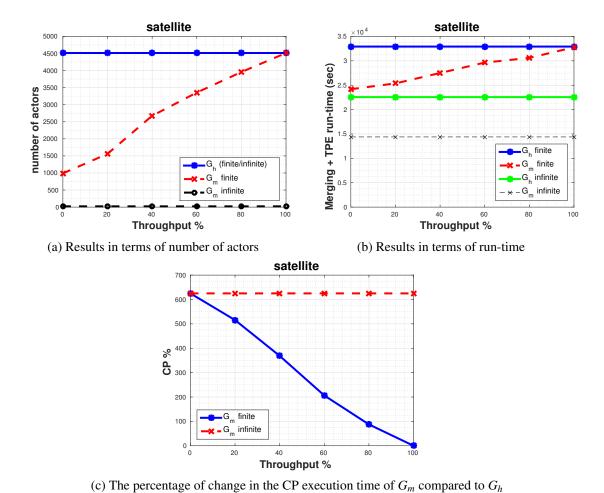

| 5.7             | satellite results                                                                   |

|                 | 5.7(a) Results in terms of number of actors                                         |

|                 | 5.7(b) Results in terms of run-time                                                 |

| <b>-</b> 0      | 5.7(c) The percentage of change in the CP execution time of $G_m$ compared to $G_h$ |

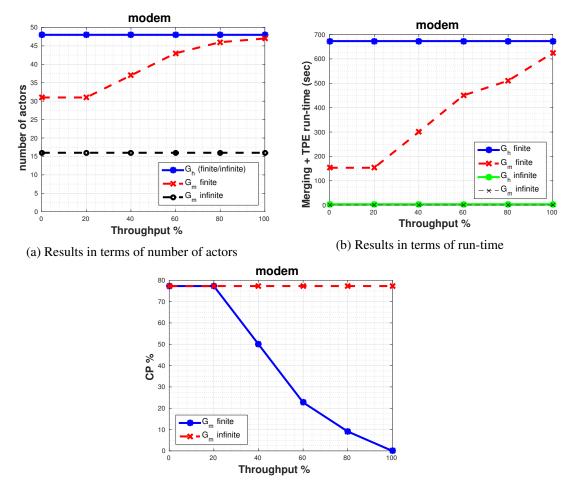

| 5.8             | modem results                                                                       |

|                 | 5.8(a) Results in terms of number of actors                                         |

|                 | 5.8(b) Results in terms of run-time                                                 |

|                 | 5.8(c) The percentage of change in the CP execution time of $G_m$ compared to $G_h$ |

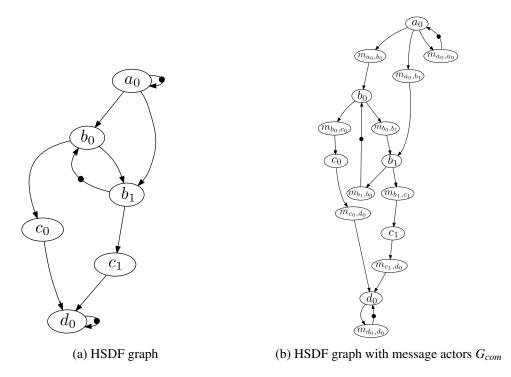

| 6.1             | Initial modelling of communication                                                  |

|                 | 6.1(a) HSDF graph                                                                   |

|                 | 6.1(b) HSDF graph with message actors $G_{com}$                                     |

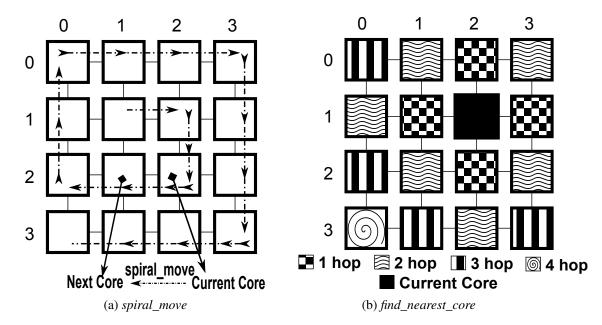

| 6.2             | Core selection methodology                                                          |

|                 | 6.2(a) <i>spiral_move</i>                                                           |

|                 | 6.2(b) find_nearest_core                                                            |

| 6.3             | Partial path classification used by SPF heuristic                                   |

|                 | 6.3(a) Class Head partial path                                                      |

|                 | 6.3(b) Class Tail partial path                                                      |

|                 | 6.3(c) Class Middle partial path                                                    |

| 6.4             | Effect of reservation bandwidth $\mathcal{R}$                                       |

| 6.5             | Evaluation of the mapping heuristic                                                 |

| 0.0             | 6.5(a) Results in terms of average number of mapped applications                    |

|                 | 6.5(b) Results in terms of run-time                                                 |

| 6.6             | Mapping results for merged and original HSDF graphs                                 |

| 0.0             | 6.6(a) Results in terms of average number of mapped applications                    |

|                 | 6.6(b) Results in terms of run-time                                                 |

|                 |                                                                                     |

# **List of Tables**

| 4.1 | SDF <sup>3</sup> benchmark applications         | 52 |

|-----|-------------------------------------------------|----|

| 4.2 | Run-time (seconds) of the algorithm             | 53 |

| 4.3 | Number of actors before and after merging       | 54 |

|     | General configuration of the experimental setup |    |

| 6.2 | SDF <sup>3</sup> benchmark applications         | 88 |

xviii LIST OF TABLES

# **List of Algorithms**

| 1 | Quick convergence Processor-demand Analysis (QPA) [Zhang and Burns, 2009a].           | 31 |

|---|---------------------------------------------------------------------------------------|----|

| 2 | Slack-based merging                                                                   | 50 |

| 3 | Extracting timing parameters of HSDF                                                  | 63 |

| 4 | Complete approach for integrating mixed application models on the same platform $\Pi$ | 79 |

| 5 | Communication-aware mapping                                                           | 81 |

| 6 | Sensitive-Path-First (SPF)                                                            | 84 |

# List of Abbreviations

ADF Affine Dataflow

BFS Breadth First Search

bps bits per second

CPF Critical-Path-First

CP Critical Path

CSDF Cyclo-Static Dataflow

DAG Directed Acyclic Graph

dbf demand bound function

DCG Directed Cyclic Graph

DF Dataflow

DM Deadline MonotonicDSP Digital Signal Processing

DVFS Dynamic Voltage and Frequency Scaling

EDF Earliest Deadline First

FF First Fit

FIFO First In First Out

GEDF Global Earliest Deadline First

HSDF Homogeneous Synchronous Dataflow

ILP Integer Linear Programming

IN Interconnection Network

MCM Maximum Cycle Mean

MLLF Modified Least Laxity First

MPAG Max-Plus Automaton Graph

NDF Non-Dataflow NoC Network on Chip

PEDF Partitioned Earliest Deadline First

P/C Production/Consumption

RM Rate Monotonic

SCC Strongly Connected Component

SDF Synchronous Dataflow

SDM Space Division Multiplexing

SADF Scenario-Aware Dataflow

SPF Sensitive-Path-First

SPP Static-Priority PreemptiveTGFF Task Graphs For Free

TDM Time Division Multiplexing

TDMA Time Division Multiple Access

TPE Timing Parameters Extraction

xxii List of Abbreviations

WCET Worst Case Execution Time

XML eXtensible Markup Language

# **List of Symbols**

#### **Task Parameters**

| τ                | A task set.                                  |

|------------------|----------------------------------------------|

| U                | A task set $\tau$ utilization.               |

| $	au_i$          | The $i^{th}$ task.                           |

| $a_i$            | The offset of $\tau_i$ (seconds).            |

| $C_i$            | The WCET of $\tau_i$ (seconds).              |

| $T_i$            | The period of $\tau_i$ .                     |

| $D_i$            | The relative deadline of $\tau_i$ (seconds). |

| $\overline{D}_i$ | The absolute deadline of $\tau_i$ (seconds). |

| $S_i$            | The arrival time of $\tau_i$ (seconds).      |

| $F_i$            | The finish time of $\tau_i$ (seconds).       |

| $U_i$            | The utilization of $\tau_i$ (seconds).       |

| $ ho_i$          | The density of $\tau_i$ .                    |

| $J_i$            | The job of $\tau_i$ .                        |

| $J_i$            | The job of $\tau_i$ .                        |

### **Feasibility Analysis**

dbf  $(t_0, t_1)$  The demand bound function within the time interval  $[t_0, t_1]$ .

Н Hyperperiod (seconds).

The upper bound on schedulability (seconds).  $t_a$

The response time of  $\tau_i$  (seconds).

The synchronous busy period of the processor (seconds).  $t_b$

The processor demand at time t (seconds). h(t)

### **Dataflow Applications**

| Datanow A | Datanow Applications                                  |  |  |  |

|-----------|-------------------------------------------------------|--|--|--|

| G         | A Synchronous Dataflow graph (SDF).                   |  |  |  |

| V         | Set of nodes (actors) in an SDF graph.                |  |  |  |

| E         | Set of edges (channels) in an SDF graph.              |  |  |  |

| $G_h$     | A Homogeneous Synchronous Dataflow graph (HSDF).      |  |  |  |

| $V_h$     | Set of nodes (actors) in an HSDF graph.               |  |  |  |

| $E_h$     | Set of edges (channels) in an HSDF graph.             |  |  |  |

| $G_p$     | A graph representing a pipeline application.          |  |  |  |

| $V_p$     | Set of nodes in a pipeline graph.                     |  |  |  |

| $E_p$     | Set of edges in a pipeline graph.                     |  |  |  |

| $G_m$     | A merged HSDF graph.                                  |  |  |  |

| $G_{com}$ | An HSDF graph with message actors.                    |  |  |  |

| d         | Set of initial tokens in a dataflow (SDF/HSDF) graph. |  |  |  |

| Γ         | Topology matrix of an SDF graph.                      |  |  |  |

|           |                                                       |  |  |  |

$\vec{q}$ Repetition vector of an SDF graph. xxiv List of Symbols

| $v_i$                                                   | The $i^{th}$ actor of an SDF graph.                                                      |

|---------------------------------------------------------|------------------------------------------------------------------------------------------|

| $v_{i_j}$                                               | The $j^{th}$ firing of the $i^{th}$ actor of an SDF graph.                               |

| $e_{ij}$                                                | A channel starting from actor $v_i$ to actor $v_j$ .                                     |

| ζ                                                       | Throughput requirement.                                                                  |

| $P_i$                                                   | The <i>i</i> <sup>th</sup> time-constrained path in an HSDF graph.                       |

| $P_i^p$                                                 | Partial path of the time-constrained path $P_i$ .                                        |

| $LP_i^p$                                                | List of partial paths in $P_i$ .                                                         |

| $\gamma_i$                                              | The sensitivity of path $P_i$ .                                                          |

| $\mathcal{D}$                                           | End-to-end deadline constraint (seconds).                                                |

| $\mathcal{D}_{xy}$                                      | Latency constraint of a time-constrained path from $v_x$ to $v_y$ (seconds).             |

| ε                                                       | laxity on a time-constrained path <i>P</i> (seconds).                                    |

| δ                                                       | Task slack (seconds).                                                                    |

| $\Omega(v_{i_j})$                                       | Set of predecessor firings of the firing $v_{i_j}$ .                                     |

| $\Phi(v_{i_i})$                                         | Set of successor firings of the firing $v_{i_i}$ .                                       |

| $\Phi(v_{i_j})$ $artheta_{i_j}$ $	heta_{i_j}$ $\hat{V}$ | Earliest start time of a firing $v_{i_j}$ (seconds).                                     |

| $\theta_{i_i}$                                          | Latest finish time of a firing $v_{i_i}$ (seconds).                                      |

| $\hat{oldsymbol{V}}^{'}$                                | Topologically ordered set of actors.                                                     |

| $\mathcal{V}$                                           | Merged cluster of HSDF actors.                                                           |

| $\mathscr{P}$                                           | Path cover for a DAG component of a $G_h$ .                                              |

| $\mathscr{O}$                                           | The set of cycles in $G_h$ .                                                             |

| $\sigma_{\!i_j}$                                        | The slack of a firing $v_{i_j}$ (seconds).                                               |

| $\mathcal{C}_k$                                         | The execution time of a cycle $k$ (seconds).                                             |

| β                                                       | A constant has a value with range $[1, \infty)$ .                                        |

| $\mathcal{P}$                                           | The set of all time-constrained paths between actors with latency constraints in an HSDF |

|                                                         | graph.                                                                                   |

| $Succ(v_x)$                                             | The list of successor actors for the actor $v_x$ .                                       |

|                                                         |                                                                                          |

## **System Model**

| Ψ                         | The system.                                                                                     |

|---------------------------|-------------------------------------------------------------------------------------------------|

| П                         | The multi-core platform.                                                                        |

| $\pi_i$                   | The $i^{th}$ core in the platform $\Pi$ .                                                       |

| n                         | One of the dimensions of the multi-core platform $\Pi$ .                                        |

| $l_{sw}$                  | The router switching latency of a single flit (seconds).                                        |

| $l_t$                     | The transfer latency of a single flit (seconds).                                                |

| ${\cal L}$                | The link capacity of IN of the platform $\Pi$ (Gbps).                                           |

| $\mathcal{R}_i$           | The fraction of the link capacity $\mathcal{L}$ reserved for an application $A_i$ (percentage). |

| h                         | The number of hops of a packet <i>p</i> .                                                       |

| $\hat{h}$                 | The maximum number of hops on IN of any packet on the platform $\Pi$ .                          |

| ${\cal F}$                | The TDM frame size (slots).                                                                     |

| $\varkappa_i$             | Number of allocated slots for application $A_i$ (slots).                                        |

| p                         | The packet size (bits).                                                                         |

| f                         | The flit size (bits).                                                                           |

| $\boldsymbol{A}$          | The application set.                                                                            |

| $A_i$                     | The $i^{th}$ application of the application set $A$ .                                           |

| $A_p$                     | A pipeline application.                                                                         |

| m                         | The size of the application set <i>A</i> .                                                      |

| $C_{i,p}$                 | The time spent by a packet $p$ of application $A_i$ traversing the IN (seconds).                |

| $C_{i,p} \ C_{i,p}^{iso}$ | The isolation time of a packet $p$ of application $A_i$ traversing the IN (seconds).            |

List of Symbols xxv

| $\hat{C}_{i,p}$ | The initial value of the WCET of a message actor (seconds).                              |

|-----------------|------------------------------------------------------------------------------------------|

| $I_i^{TDM}$     | The TDM interference time of any packet from application $A_i$ traversing the IN (sec-   |

|                 | onds).                                                                                   |

| $I_i^{TDM.co}$  | The TDM interference time of any packet from application $A_i$ traversing the IN, assum- |

|                 | ing continuous slot assignment policy (slots).                                           |

| ${\cal G}$      | The IN frequency.                                                                        |

# Chapter 1

# Introduction

We are living the golden age of ubiquitous computing. If we look around, we will find ourselves surrounded by computing devices embedded in systems that help or serve us in our daily life. These systems ranges from simple portable gadgets, e.g. smartphones, cameras, gaming consoles, to large complex systems, e.g. airplanes, cars, industrial automation. These systems are called *embedded systems*.

An embedded system can be broadly defined as a computing system that performs a dedicated function within a larger system [Jiménez et al., 2014]. This dedicated function is not designed to be programmed by the end user as functions in general purpose computing [Heath, 2002]. The concept of computing systems performing dedicated functions is old going back in time preceding the concept of a general-purpose computer [Jiménez et al., 2014]. If we look at the earliest forms of computing devices, they adhere better to the definition of an embedded system (in terms of performing a dedicated function) than to that of a general-purpose computer. An example of these devices is the Colossus computer [Copeland, 2006], which refers to a series of computers developed by British code-breakers in 1943-1945. Colossus dedicated function was to help in the cryptanalysis of the German teleprinter messages during World War II.

At early stages, embedded system designs used microcontrollers as a main processing unit, since the application demands were simple. Following the rise in application demands and growing complexity, many embedded systems incorporate multi-core processor architectures for satisfying the increasing demands of its applications, since the need for high processing power at a low power budget is a great concern for such systems [Kim et al., 2010]. A real life example of this trend is the cellular phone. At the beginning, the first generation of cellular phones incorporated a single core digital signal processor chip [PratapSingh and Kumar Jain, 2014], since its main dedicated function was making phone calls. However, the latest generations feature at least a quad-core multi-processor at least, e.g. Samsung Galaxy S7 smartphone incorporating Qualcomm<sup>®</sup> Snapdragon<sup>TM</sup> 820 processor [Qualcomm, 2016]. This is because the cellular phone has become a portable computer, multimedia and connectivity device.

The trend of the growing functionality of embedded systems can be demonstrated by the various types of applications that run simultaneously on the system [Jiménez et al., 2014]. These ap-

2 Introduction

plications may have different requirements, such as computational demands or timing constraints. For example, the cellular phone runs a time-constrained application, which is the phone call, along with computationally intensive ones, such as multimedia and gaming applications. The fact that embedded systems run various applications with different requirements can mean different applications may be represented using different computational models. In such systems running mixed computational models, guarantees are required to assure stratifying requirements (computational demands or timing constraints) and the correct execution of the system, especially in case of safety-critical applications. A current example of such systems is high-end cars, which may run an advanced multimedia entertainment system (that requires huge computational resources) along with the autonomous driving function (safety-critical application) that allow self-driving on the highways, i.e. Tesla Model S, X and 3 [TESLA, 2016].

Embedded systems running mixed computational models is an increasing futuristic trend, since embedded systems are included in almost every device. In this thesis, we are concerned with embedded systems that incorporate mixed computational models with timing constraints running on the same multi-core platform. These computational models are dataflow with timing constraints and traditional real-time task sets, since they represent a wide range of applications running on top of embedded systems. The dataflow computational model represents Digital Signal Processing (DSP), Streaming and multimedia applications, while traditional real-time computational model covers a wide range of time-constrained applications with different levels of criticality. Example of future embedded systems that run these two computational modes are Autonomous Driving Systems [Elliott et al., 2014] and Unmanned Air Vehicles [Zhou and Wu, 2006]. These kind of systems require real-time guarantees that all running applications will execute safely without missing their deadlines. Also, they require efficient use of system resources to minimize the overall cost of the system.

We begin this thesis by briefly introducing the two computational models considered in this thesis. They are the real-time computational model (Section 1.1) and the dataflow computational model (Section 1.2), where we detail the parameters and the properties of each model. Then we follow by presenting an overview of processing platforms and architectures in Section 1.3. After these introductory sections, we introduce our problem statement in Section 1.4, followed by a detailed proposed solution explaining its functionality in Section 1.5. Finally, we end this chapter by summarising our thesis contributions and providing the thesis organisation in Sections 1.6 and 1.7, respectively.

### 1.1 Real-time Computational Model

A **real-time computational model** is a computing paradigm used to define a certain set of applications that have to respond to externally generated input stimuli within a finite and specified period of time [Buttazzo, 2004, Krishna, 1996]. The main characteristic that distinguishes real-time computing from other types of computation is time, because the correct execution of the applications of such computational model depends not only on the logical result but also on the

time it is delivered. The instant when a result must be produced is called a *deadline*. Failure to respond within the specified timing interval or a delayed response could be useless or even have fatal consequences. Based on these consequences, the real-time computational model classifies its applications into three categories [Buttazzo, 2004, Krishna, 1996]:

**Hard real-time:** An application is considered **hard real-time** if missing its deadline during execution may cause catastrophic consequences on the system under control, surrounding environment or people.

**Firm real-time:** An application is considered **firm real-time** if missing its deadline during execution is useless for the system, but does not cause any damage.

**Soft real-time:** An application is considered **soft real-time** if missing its deadline during execution has still some utility for the system, although causing performance degradation.

These are the three basic categories of applications according to the real-time computational model. There exist other classifications that branch from these basic categories. Whatever their category, all the applications in this computational model are called *real-time applications*. In the following section, we will shed more light on real-time applications and its different criteria classifications.

### 1.1.1 Real-time Applications

Real-time applications are wide-spread in daily life systems, e.g. telecommunications, aviation, nuclear reactors, autonomous driving systems, industrial automation. A real-time application can be modelled as a finite set of simple, highly repetitive entities that are recurrent in nature called real-time *tasks* [Baruah and Goossens, 2004]. Each instance of a task is a basic unit of work that executes on the processing platform and is called a *job* [Liu, 2000]. A real-time task has different classifications based on its timing parameters. In the following section we discuss that in details.

#### Real-time task classification:

A real-time task has several classifications that vary based on the criteria used. In this thesis, we are concerned with two criteria in real-time task classification. First, the frequency of which a task instantiates its jobs (task periodicity) classifies a real-time task into three categories [Isović and Fohler, 2000]:

**Periodic tasks:** A task that releases its jobs periodically after a fixed time interval is defined as a periodic task. The fixed duration between the two consecutive jobs releases is called the period of the task.

**Sporadic tasks:** A task that releases its jobs at some arbitrary time instant but two consecutive jobs of a task are always separated by at least a predefined time interval called the minimum inter-arrival time.

4 Introduction

**Aperiodic tasks:** Jobs of an aperiodic task are not constrained by a minimum interarrival time or a period, the task can release jobs at any instant.

Periodic tasks are the most well-known model in real-time systems. Sporadic tasks can be converted into periodic tasks with a predefined minimum interarrival time [Buttazzo, 2004]. Aperiodic tasks can be handled using periodic server-based systems with budget. The server is modelled as a periodic task. The server can serve aperiodic tasks until the budget expires. The budget can be replenished every period [Sprunt, 1990].

Second, real-time tasks are always constrained with a timing requirement. A task should complete its execution within a predefined time interval called the *relative deadline*. The *relative deadline* of a task depends on the nature of an application. For example, the object recognition/detection application in an autonomous driving system has a relative deadline in terms of a few microseconds, while a room temperature monitoring application in an air conditioning system can have a relative deadline in terms of a few seconds. The *relative deadline* of a real-time task, whether it is periodic, sporadic or aperiodic, can be categorized into three main categories [Buttazzo, 2004, Krishna, 1996]:

**Implicit-deadline task model:** has a relative deadline equal to its period or minimum inter-arrival time.

**Constrained-deadline task model:** may have a relative deadline less than or equal to its period or minimum inter-arrival time.

**Arbitrary-deadline task model:** has a relative deadline that has no relation with the period or minimum inter-arrival time of a task. This means that the relative deadline can be set to any value regardless the value of the task's period.

In this thesis, we are concerned with real-time systems running periodic arbitrary-deadline tasks.

#### 1.1.2 Worst-Case Execution Time

The execution time of a real-time task is an important parameter that defines its temporal behaviour. Different jobs of a task exhibit variation in their execution time depending on the hardware characteristics, structure of the software, input data and different behaviour of the environment with which the jobs are interacting. In order to guarantee the temporal correctness, the upper bound on the execution time of a task, referred to as the Worst-Case Execution Time (WCET), is specified. The WCET of a task is a safe upper bound greater than or equal to the longest execution of any job released by the task, under worst-case input conditions without interference from other tasks. Any miscalculation of WCET may cause a system failure depending on, whether or not, the system is a hard real-time. There are several methodologies and techniques to determine the WCET of a task detailed in [Puschner and Burns, 2000, Wilhelm et al., 2008] for further reading. Real-time system designers consider the WCET of tasks while designing a system to guarantee the timing properties. However, different jobs of a task may execute for less than their WCET

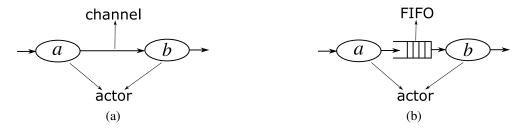

Figure 1.1: Dataflow application.

leaving behind unused computing resources. This bound is almost always pessimistic to be safe. Jobs hence typically execute faster.

### 1.2 Dataflow Computational Model

The dataflow computational model [Chamberlin, 1971, Estrin and Turn, 1963, Rodrigues, 1969, Shields, 1997] is a well-known, simple, and powerful model of parallel computation. In this model, there is no notion of a single point or locus of control corresponding to the conventional sequential computing. However, it models an application as a set of tasks with data dependencies. It is a very useful specification mechanism for signal processing systems since it captures the intuitive expressiveness of block diagrams, flow charts, and signal flow graphs, while providing the formal semantics needed for system design and analysis tools.

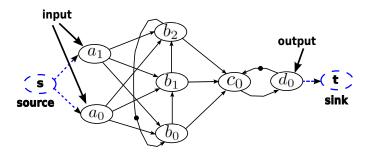

### 1.2.1 Dataflow Applications

A dataflow application is a directed graph, where the vertices represent computation tasks and edges represent First-In First-Out (FIFO) queues that direct data values from the output port of one computation task to the input port of another. Hence, a dataflow application can be considered a set of computation tasks with dependencies. The graphs' vertices (computation tasks) are called *actors*, while its edges (FIFO queues) are called *channels*. Channels thus represent data dependencies between actors.

A dataflow application executes by performing the functions defined by its actors. An actor can be a single instruction, or a sequence of instructions, since the dataflow model does not imply a limit on the size or complexity of actors. Initially, an actor is an idle task. Its execution is triggered once the required amount of data arrives on its input ports. The amount of input data is specified by each actor according to its functional requirements. Many actors may be ready to execute simultaneously, and thus represent many asynchronous concurrent computation events. An actor starts execution by consuming data from its corresponding input ports, performing computations, and then produce a certain amount of data on its output ports. The execution process of an actor is called a *firing*, while the data produced or consumed in the firing process are referred to as *tokens*.

Figure 1.1 shows an example of a dataflow graph, that consists of actors (a, b) and the channel between them represented as a FIFO queue that direct tokens from the output port of actor a to the input port of actor b. Initially, actors a and b are idle. Once the required tokens are available

6 Introduction

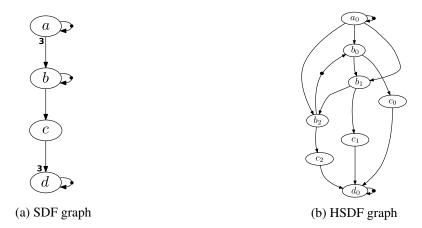

Figure 1.2: Example of SDF and HSDF graphs.

on the input port of actor a, it consumes them, starting the firing process, then produces tokens on its output port. The tokens produced are transferred to the input port of actor b through the FIFO channel, triggering its firing process that results in producing tokens on its output port similar to actor a. The functions performed by the actors define the overall function of the dataflow graph. For example, Figure 1.1 could represent a water level control system, where actor a is measuring the current level of water in a tank and send signals to actor b that controls the operation of the water pump.

A dataflow application has three important timing parameters, they are:

**Execution time of its actors:** an actor may have different values of execution time. This may be due to different tokens consumed, which triggers different functions to be executed inside the actor. Also, it may be due to the same reasons a real-time task faces that are mentioned previously in Section 1.1.2. However, for predictable execution behaviour and analysis purposes, the execution time determined for each actor represents an upper bound (WCET) to all of its firing modes. The calculation of WCET is mentioned earlier in Section 1.1.2.

**Throughput:** is an important constraint and crucial indicator of performance for dataflow applications. The throughput of a dataflow application refers to how often an actor produces an output token. To compute throughput, the WCET of the firing of each actor has to be measured and an execution scheme must be defined. The execution scheme is the self-timed execution of actors, where each actor fires as soon as all of its input data are available [Sriram and Lee, 1997].

**Latency:** is a timing constraint that defines a time bounded interval between firings of two actors in the dataflow application. It can be realised as a relative deadline for the firings that happen between these specific two firings.

There exist several dataflow computational models, e.g. Synchronous Dataflow (SDF), Homogeneous Synchronous Dataflow (HSDF) [Lee and Messerschmitt, 1987b], Cyclo-static Dataflow (CSDF) [Bilsen et al., 1995], Scenario-Aware Dataflow (SADF) [Theelen et al., 2006], where each model have its own specifications and rules that enable capturing wide range of applications. However, we focus on those that can be described by SDF and HSDF [Lee and Messerschmitt, 1987b].

**SDF:** is useful for modelling and analysis of Digital Signal Processing (DSP) and concurrent multimedia applications [Lee and Messerschmitt, 1987b, Poplavko et al., 2003, Sriram and

Bhattacharyya, 2000, Wiggers et al., 2007], where they represent computations on an indefinitely long data sequence. This is because of the ability to obtain periodic schedules for the SDF execution where actors fires a determined number of times with a specific order, in a cyclic manner, where each cycle called an *iteration*. Every actor in an SDF graph consumes/produces a fixed number of tokens every time it fires. The SDF graphs are accompanied with several timing analysis techniques, which are used for evaluating performance metrics of such applications, most importantly throughput. Figure 1.2(a) shows an example of an SDF graph that consists of two actors a and b. Actor a represents a source task that produces two tokens every time it fires (denoted on its output port), while actor b represents a sink task that consumes a single token every time it fires (denoted on its input port). The periodic schedule for such SDF graph is (a, b, b), because actor a produces two tokens that triggers actor b to fire twice consuming a single token each.

HSDF: is a more restricted model of SDF, where actors consume/produce a single token every time they fire. Each actor in an HSDF graph fires once during an iteration of the graph. This restriction allows HSDF graph to reveal the parallelism hidden in applications represented using more expressive models, e.g. SDF, CSDF. For example, Figure 1.2(b) shows an HSDF graph representation of the SDF graph shown in Figure 1.2(a). As we notice, the HSDF graph reveals the parallelism hidden in the SDF graph by showing actor *b* firing twice simultaneously (*b*<sub>0</sub>, *b*<sub>1</sub>). Many dataflow graphs expressive models, e.g. SDF, CSDF, can be converted to an equivalent HSDF graph by using a conversion algorithm, such as the one presented in [Sriram and Bhattacharyya, 2000]. Although transformation to HSDF allows revealing the parallelism in dataflow applications, it can lead to an exponential increase in the size of the original dataflow graph [Lee and Messerschmitt, 1987a, Sriram and Bhattacharyya, 2000], which may result in a significant increase in the run-time of many dataflow analysis algorithms, e.g. throughput analysis, as described in the following chapters. Further details on SDF and HSDF are given in Chapter 3.

### 1.2.2 Streaming Applications

Streaming applications constitute a huge application space for embedded systems. They are becoming increasingly important and widespread, since they run on many common devices and systems that affect our daily life. A common well-known example of this in daily life is the smartphone, as shown in Figure 1.3(a). It is a multi-purpose (i.e., communication, entertainment, navigator, etc.) embedded system that runs several streaming applications with different purposes that ranges from communication to entertainment. Another example considered as safety-critical is Autonomous driving systems, shown in Figure 1.3(b), that have started to be integrated in many car driving systems (e.g. Google, Tesla, Mercedes, etc.). These systems enable cars to sense their environment, navigate without human input and stay connected to the Internet [Gehrig and Stein, 1999]. Both of these example systems process audio and video streams on which streaming applications perform functions like audio/video encoding and decoding, object recognition, object

8 Introduction

(b) Autonomous driving systems [Daily Autonomous Car News, 2015] .

(a) Smartphones [Kenya Tech News, 2015].

Figure 1.3: Examples of embedded systems running streaming applications.

detection and image enhancement on the streams [Elliott et al., 2014, Salunkhe et al., 2014, Siyoum et al., 2011]. These kind of streaming applications have *high processing requirements* and *timing constraints* that must be satisfied, especially in case of safety-critical applications.

The *high processing requirements* raises the need for a parallelization model to enable applications to use massive computational power [Pankratius et al., 2009], which the dataflow model of computation is able to achieve for streaming applications [Lee and Messerschmitt, 1987a]. This is because dataflow model is inherently parallel and can work well in decentralized systems. Furthermore, since these applications are basically a series of transformations that are applied to a data stream, the dataflow model is a natural paradigm for representing them for concurrent implementation on multi-/many-core processors [Lee and Messerschmitt, 1987a].

The streaming applications' *timing constraints* require guarantees that they will be satisfied during applications execution. Recently, several works applied real-time scheduling and analysis techniques on dataflow applications [Bamakhrama and Stefanov, 2011, 2012, Di Natale and Stankovic, 1994, Kao and Garcia-Molina, 1997, Lipari and Bini, 2011, Liu et al., 2014, Saifullah et al., 2011]. However, they are limited to dataflow applications represented as Directed Acyclic Graphs (DAG) or implicit-deadline task models, which discards a wide range of dataflow applications.

### 1.3 Processing Platform

This section aims to discuss different processing platform architectures and features of interconnection network. The main goal is to explain the specifications of the processing platform assumed in this thesis.

The processing platform refers to the hardware responsible for running applications in the real-time embedded system. There is a paradigm shift towards multi-/many-cores in the design process of processing platforms. Presently, increasing the number of cores is the current way to

improve the performance for high-end processors rather than increasing the clock speed for single processors. One of the reasons why the clock rate gains of the past cannot any more be continued is the unsustainable level of power consumption [Vajda, 2011].

#### **Architecture:**

A multi-/many-core platform has more than one core or processor. These cores can be similar or completely different in architecture. Consequently, multi-/many-core platforms can be categorised into two main types based on the relation between the cores on a given platform:

Homogeneous Architecture: in this architecture type all cores in the platform are identical and have exactly the same properties in terms of computation (e.g. instruction set, frequency and cache size) and the cores are interchangeable. The execution time and energy consumption of a task remains the same on all cores on such a platform. These platforms are also sometimes called symmetric multi-processor platforms (SMP). Many platforms manufactured and deployed today in embedded systems fall under this category. For example, Cortex-A17 [Cor] from ARM (used in smart phones, tablets, smart TV's, etc.) has four identical cores on a same die.

**Heterogeneous Architecture:** this architecture type features at least two different kinds of cores that may differ in both the instruction set architecture, frequency and cache size. The most widespread example of a heterogeneous multi-core architecture is the Cell BE architecture, jointly developed by IBM, Sony and Toshiba [Gschwind et al., 2006] and used in areas such as gaming devices and computers targeting high performance computing.

### **Interconnection Networks (IN):**

Since increasing the number of cores in multi-/many-core platforms is the current trend to increase the performance, there should be an efficient communication network to connect them, called Interconnection Networks (IN). The IN between multiple cores may be a performance bottleneck, since it is responsible for transferring and routing of data between different cores. These data are in the form of packets with headers that contain information about its destination. Data transfer between distant cores can increase latency and consume extra power. In the following paragraphs, we look at traditional IN topologies.

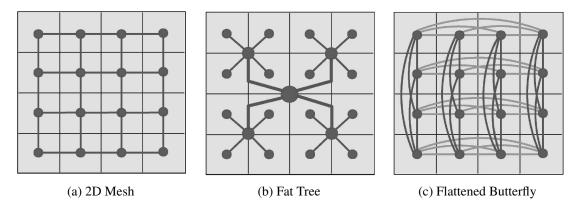

**2D-Mesh:** shown in Figure 1.4(a), is a common topology that uses routers that are connected to other routers as well as a number of cores. Advantages include design simplicity and short links. Disadvantages include a potentially high number of hops.

**Fat Tree:** shown in Figure 1.4(b), is a tree topology where the cores are located at leaves of a tree and internal nodes are routers. Data travels upward in the tree until a common ancestor is found between source and destination. The number of links increases towards the root of the tree. Advantages include high bandwidth because of the increased number of links

10 Introduction

Figure 1.4: Examples of Interconnection Networks (IN) [Sanchez et al., 2010].

as data moves towards the root. Disadvantages include the need for more complex routers, again because of the increased number of connections toward the root.

**Flattened Butterfly:** shown in Figure 1.4(c), is a modified butterfly network that is essentially a mesh network with additional links. Advantages include a small number of hops. Disadvantages include complex routers and increased chip area due to the large number of links.

#### **Routing:**

In all IN topologies, except fully connected topology, not all the router-pairs are directly connected. Therefore, in such cases, depending on the position of the sender and the receiver, packets may need to travel across multiple intermediate links and routers. A set of traversed network elements (routers and links) is called the *route*, while the number of traversed links is usually referred to as the *number of hops*.