Quicknews

Don't forget to check the summary of our activities at our Annual Reports Archive

2019

1. +Science +Europe

2. Portugal Space visit to Airbus Defence and Space (ADS)

3. VORTEX, the Collaborative Laboratory in CPS, was officially launched

4. VORTEX Bootcamp in CISTER

5. VORTEX General Assembly

6. Final Event of the ENABLE-S3 project in Graz, Austria

7. Another Successful Industry-Driven Project delivered

8. THERMAC physical kick-off meeting at CISTER

9. General Assembly and F2F meeting of the project SCOTT in Gdansk, Poland

10. REASSURE progress meeting at U.Minho

11. Open Debate Session about "Plasticology" at Porto Design Factory

12. A Machine Learning challenge was won by CISTER interns

13. HDR examination of Luca Santinelli

14. Visit from Serbian Researcher of the RT-RK National Research Institute

15. Periodic Seminar on "the Interaction-Centric Paradigm"

16. PhD student from Universidad de Alcalá invited to give a talk on "Digital Communications for the Control of Modular Multilevel Converters" at CISTER

17. Periodic Seminar on Security in Embedded Systems

18. Periodic Seminar on Thermal-Aware Scheduling

19. Periodic Seminar on "Effective System Integration"

20. Distinguished seminar on Model-Driven Engineering

21. Distinguished Seminar on Communications for Satellites

1. CISTER leads new longer-term contracts with researchers

2. CISTER participated in Portuguese delegation led by Minister Manuel Heitor at Carnegie Mellon University (CMU)

3. Participation in new CPS CoLab meeting in Lisbon

4. CISTER Researchers partipated on ECS Brokerage event, in Brussels

5. CISTER Researcher attended the F2F technical board meeting of the project SCOTT

6. CISTER Researchers participated in the Flexigy Workshop, in Coimbra

7. Scientific Council Meeting

8. Two new PhD members recently joined CISTER

9. Four new PhD students have joined CISTER

10. CISTER Researchers attended the seminar on "Analysis, Design, and Control of Predictable Interconnected Systems"

11. CISTER Junior Researcher: Talk A Bit 2019

12. Training on "Introduction to Real-time Systems"at CISTER Facilities

13. Pedro Miguel Santos gave a talk on Vehicular Networking and Urban Sensing Platforms

14. Giann Nandi gave a talk on Formal Verification of Cryptographic Protocols

15. José Fonseca successfully defended his PhD thesis at FEUP

16. Distinguished Seminars by Scientists from University of York and from Politecnico di Milano

2018

1. Nomination for Associate Editor for IEEE Access Journal

2. Participation in the International Forum EFECS 2018, in Lisbon

3. 5th edition of AED Days, in Oeiras

4. CISTER has great participation in RTSS 2018

5. SCOTT General Assembly in Cork, Ireland

6. Last General Assembly of ENABLE-S3 project

7. Another successful PhD thesis defense

8. Director from Cyspri Lab, in Australia, gave a talk on Security in Internet of Things, at CISTER

9. In Memoriam: José Rufino (1958-2018)

1. A Re-energized CISTER

2. Celebrating 20 Years

3. Sustained Growth

4. Outlook

5. Research Projects Starting in 2018

6. 5 PhD Students already Graduated in 2018

7. Feeding the International PhD Students' Pipeline

8. Creating of the Vortex CoLab

9. Porto as the epicenter of Cyber-Physical Systems

10. CISTER Brief Quicknews

11. In Memoriam

1. Outstanding Paper Award at ECRTS 2018

2. Ramiro Robles participated in the SCOTT project review

3. PhD student Miguel Gaitán participated in the Summer School on Control and Robotics at FEUP

4. 6 international PhD Students joined CISTER

5. Benny Åkesson gave a distinguished seminar on Certifiable Resource Sharing in Safety-Critical Multi-Core Real-Time Systems

6. Ana Aguiar gave a distinguished seminar on IoT for Smart Cities

7. Undergraduate students Joel Pinto and Rúben Gonçalves presented a talk on Analysis of RTEMS in multi-core platforms

8. Undergraduate student Renato Oliveira presented a talk on Emulation library for a CPS simulation platform

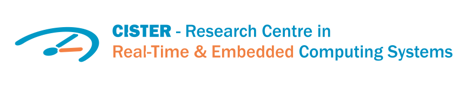

1. CISTER hosts in Porto, the largest event on Cyber-Physical Systems, CPS Week 2018

2. Ramiro Robles participated in the ISO/IEC/JTC1 SC41 meeting in Berlin

3. Ricardo Severino participated in the annual review meeting of the SafeCOP project in Brussels

4. SCOTT project wins “Best Project Presentation and Communication Award”

5. Michele Albano gave a Keynote presentation at the MPMM 2018

6. André Pedro successfully defended his PhD thesis titled “Dynamic contracts for verification and enforcement of real-time systems properties” at UMinho in Braga

7. Luis Pinto successfully defended his PhD thesis titled “Aerial Multi-Hop Sensor Networks” at FEUP in Porto

8. Zahid Iqbal successfully defended his PhD thesis at FEUP

9. António Barros successfully defended his PhD thesis at FEUP

10. PhD student Ishfaq Hussain presented a talk on Multicore Processors for Resource-Aware Applications

11. PhD student José Fonseca presented a talk on Response Time Analysis in Global FP Scheduling

12. Reinder Bril gave a distinguished seminar on WCRT Analysis in Ethernet AVB

13. Moris Behnam gave a distinguished seminar on Predictability and dependability in parallel architectures

1. Gaming app from EnerGAware project released in app stores

2. General assembly of the MANTIS Project

3. Luis Miguel Pinho presented results of CISTER projects at HiPEAC 2018 conference in Manchester

4. CISTER Researchers participated in the KhronoSim project meeting at Critical Software

5. Paper co-authored by Alan Burns and Borislav Nikolic won the Best Paper Award 2018

6. PhD student Mubarak Ojewale presented a talk on a Intelli-Fog Approach for Data in IoT

7. PhD student Miguel Gaitán presented a talk on Information-Centric Networks for IoT

8. CISTER Researcher Patrick Yomsi presented a talk on Real-Time Data in Mobile Intelligent Transportation

9. CISTER Researcher Patrick Yomsi presented a talk on Real-Time Data in Mobile Intelligent Transportation

10. Antonio Augusto Fröhlich (UFSC - LISHA) presented a Distinguished Seminar on SmartData for a Trustful Internet of (Cyber-Physical) Things

11. Karl-Erik Årzén (Univeristy of Lund) presented a Distinguished Seminar on Control of and over the Cloud

2017

1. European Association on Higher Education visits CISTER

2. CISTER Industry Seminar with João Rodrigues

3. Keynote given in Brazilian Symposium on Computing Systems Engineering

4. CISTER researcher is now an ACM distinguished speaker

5. CISTER Member plays key role in shaping IEEE program for young professionals

6. Conclusion of the 2017 Summer Internship

7. Another student graduates with highest honours

8. CISTER soon to welcome new research scholars

1. CISTER holds General Assembly of Project on Security, Trust and Privacy of Industrial IoT

2. PT2020 project on Smartgrid moves ahead

3. CISTER welcomes DSR Corporation to Porto

4. Portuguese Aeronautics, Space and Defence Cluster visits CISTER

5. CISTER Researchers Gather Best Paper Award at Real-Time Conference

1. Celebrating Two Decades of Cyber Physical Systems in Portugal

2. Key European players will discuss Secure and Trustable Industrial IoT in CISTER

3. EMC2 – the successful story of one of the largest European ICT projects on Embedded Real-Time Computing Systems

4. Results of successful FP7 project lead by CISTER presented to key academic and industrial European institutions at EMC2’s Safety Critical Systems Workshop

5. CPS Week 2018 preparations in full swing

6. Patent on vehicle platooning accepted

7. Discussing the Improvement of the Digitization of European Industry - CISTER Holds meeting of the largest European project to date

8. First CISTER Summer Internship in Progress

1. Portuguese industry boosts competiviveness with new collaborations in Paris Air Show

2. CISTER is partner of the newly approved 48MEuros K2 Digital Mobility Project

3. CISTER participates in the Portuguese Agenda for Science and Innovation in Cyber-Physical Systems

4. Porto with enhanced IoT/Embedded ecosystem

5. ECRTS conference sees strong CISTER presence in Dubrovnik

6. Invited Talk at Safety Critical Systems Workshop

7. WFCS program committee co-chaired by CISTER researcher

8. RTSS 2017 TPC Meeting in Paris

9. A new collaboration between CTU Prague and CISTER

10. Book on Robot Operating System tops Springer List

1.CISTER Celebrates 20 Years

2.Digitalization of the European Industry: the start of the EU Project Productive 4.0

3.Start of European Project SCOTT: Building Trust in the Internet of Things

4.CISTER Leads Dependable Wireless Technologies for Aeronautics

5.The Arrowhead Project on IoT Automation Concludes in Style

6.Congratulations Hazem Ali for your PhD!!!

7.Innovation for Safe and Secure Highly Automated and Autonomous Systems

8.New Book on Operating Systems for Unmanned Aerial Vehicles

9.Distinguished Seminars by Scientists from TNO and Max Planck Institute

1.CISTER Celebrates 20 Years

2.Digitalization of the European Industry: the start of the EU Project Productive 4.0

3.Start of European Project SCOTT: Building Trust in the Internet of Things

4.CISTER Leads Dependable Wireless Technologies for Aeronautics

5.The Arrowhead Project on IoT Automation Concludes in Style

6.Congratulations Hazem Ali for your PhD!!!

7.Innovation for Safe and Secure Highly Automated and Autonomous Systems

8.New Book on Operating Systems for Unmanned Aerial Vehicles

9.Distinguished Seminars by Scientists from TNO and Max Planck Institute

1. Happy New 2017

2. CISTER fosters stronger relationship with former researchers

3.CISTER Participation in ECSEL project, Productive 4.0

4.Results of P-SOCRATES project presented in Stockholm

5. Book on IoT Automation

6.Next ENABLE-S3 General Assembly at CISTER

7.PEMAS visits CISTER

8. Artemis/ECSEL Brokerage event

9.New research student call

2016

1. Industry Experts gather in Porto for P-SOCRATES Industrial Workshop

2. RTSS2016 - a huge success

3. ENABLE-S3 General Assembly in Madrid

4. CIWORK 2016

5. Visit of collaborator from Universidad Carlos III Madrid

6. PC meeting of RTAS’17 organized in CISTER

1. KhronoSim Project Kicks Off

2. Mantis Reaches First Milestone

3. Arrowhead Project is Coming To A Successful End

4. ISO/IEC JCT 1/WG7 Meeting Held in China

5. ICT Proposers Day 2016

6. CISTER Successful in ECSEL Call

7. CISTER Researcher Program Co-Chair at RTCSA

8. CISTER Researcher Program Co-Chair at RTNS

9. New Visiting PhD Student at CISTER

10. The Return of a Past Member and Other CISTER Graduates Moving On

11. Another Season of the Periodic Seminar Series Begins

1. DSGrid kick-off meeting held

2. Portuguese Railway Platform initiative - Meeting with Evoleo

3. The EnerGAware project - Serious Games for Energy Efficiency

4. CISTER participates in European roadmap in High-Performance Embedded Computing

5. P-SOCRATES technical meeting held

6. ECSEL ENABLE-S3 technical meeting held

7. RTSS 2016 is around the corner

8. Another successful PhD defense

9. Book on Memory controllers for Mixed-Time-Criticality Systems

10. CISTER participates in Ciência 2016

11. CISTER PhD students complete internships abroad

12. Another international researcher joins CISTER

13. CISTER hosted another distinguished seminar

14. CISTER participates in the 16th INESC-TEC’s Football Tournament

15. Visit of collaborator from ONERA

1. Final review of CONCERTO project

2. Initiatives for cooperation: The Smart Anything Everywhere initiative and the Advanced Computing and CPS Collaboration Workshop

3. ECSEL ENABLE-S3 kick-off meeting held

4. CISTER researchers achieve outstanding results in ECRTS conference

5. TACLe Summer School 2016

6. CISTER researcher co-chairs ADA-Europe

7. Visit of collaborator from Mälardalen University

1. PT2020 proposal DSGrid accepted

2. CISTER in collaboration with EMBRAER

3. CISTER participates in ECSEL call

4. GMV visits CISTER

5. Arrowhead Project progresses

6. CISTER researcher invited lecturer at FCUP

7. CISTER Researcher invited speaker at conference

8. Visit of collaborators from Lulea University of Technology

1. Kick Off meeting of ECSEL project SafeCOP

2. CISTER-led HiPEAC CSW thematic session

3. Review meeting of DEWI

4. ECSEL/Artemis-IA Spring Event

5. High participation of CISTER in H2020 calls

6. CISTER European Project presented to European Commissioner for Research, Science and Innovation

7. Another successful PhD defense

8. Multifaceted participation at CPS Week 2016

9. Two international PhD students join CISTER

10. CISTER hosted two distinguished seminars

11. ACM SIGBED meeting in Vienna

12. Visit to CISTER by the Dean of the Faculty of Creative Industries

1. Visit to CISTER by the Minister of Science, Technology and Higher Education

2. P-SOCRATES showcases results to the industrial advisory board

3. Collaboration between Arrowhead and MANTIS ECSEL projects

4. CISTER successful in ITEA call

5. CISTER hosts ISO/IEC working group meeting

6. Visitors at the Centre

1. Celebrating 4 years of CISTER facilities

2. CISTER to host RTSS 2016

3. CISTER Participation in European Projects

4. CISTER-led European Project meets at HiPEAC 2016

5. New Initiatives

6. Multiple PhDs from CISTER’s ranks

7. CISTER hosted two distinguished seminars

1. CISTER keeps international leadership in real-time and embedded systems

2. Successful finish of CarCoDe project

3. Multiple PhDs from CISTER’s ranks

4. CISTER researcher organizes lectures in Lulea University of Technology

5. Awards and recognition at conferences

6. CISTER signs MoU with Embraer

7. CiWork 2015

8. Successful results in ECSEL call

9. CISTER hosts last TACLe COST Action Meeting

2015

1. Multiple Projects move ahead

2. Another PhD from CISTER’s ranks

3. Awards and recognition at conferences

4. Visit by Brazilian universities

5. Participation in INFORUM 2015

6. CISTER participates in ASHLEY workshop

7. CISTER participates in ICT 2015

8. Kickstart of 2015-16 periodic Seminar Series

9. Publication of WSN book in Arabic

1. New Members and Visiting Professors

2. CISTER Projects progress

3. Eduardo Tovar elected vice-chair of ACM SIGBED

4. Embraer visits CISTER

5. CISTER Scores Best Paper Award

6. CISTER progresses in ECSEL and PT2020

1. CISTER joins PEMAS Aerospace association

2. Three successful PhD defenses

3. FCT/ANI talk on H2020 and ECSEL performance and opportunities

4. CISTER participates in TCRTS workshop on CMAS

5. CISTER participates in ARTEMIS CO-SUMMIT

6. P-SOCRATES Technical Meeting in Zurich

7. ARCS 2015: a huge success

8. DEWI Project Review Meeting in Brussels

1. High participation of CISTER in FCT calls for R&D projects

2. CISTER moved several international projects forward

3. EnerGAware Project Kicks-off in Barcelona

4. HiRES Workshop at HiPEAC 2015

5. EWSN 2015: a huge success

6. SmartCities Workshop @ EWSN 2015

1. Invited seminar in one of the leading research labs in Europe

2. Towards the second milestone of P-SOCRATES

3. A new visiting scholar for CISTER

4. A rich and captivating program envisaged for EWSN 2015

5. CISTER advances its smart city initiatives

6. ECSEL project proposal enters negotiation phase

2014

1. CISTER participates in H2020 project EnergAware accepted in highly competitive call

2. CISTER researchers chair the 8th Junior Researcher Workshop on Real-Time Computing (JRWRTC)

3. CISTER-lead European project P-SOCRATES meets in Porto

4. Largest European R&D project in the area of wireless sensor networks and wireless communication visits Porto

5. Two talented PhD candidates joined CISTER/INESC-TEC

6. Horizon 2020 Infoday

7. Another PhD from CISTER’s ranks

2. Final results of the BIC students (interns) at CISTER

3. High participation of CISTER in ECSEL JU Calls

4. 2nd CISTER Industrial workshop: CiWork 2014

5. CISTER visited by representatives of Embraer

6. CISTER hosted another distinguished seminar in September from Prof. Frank Mueller

1. CISTER hosted a distinguished seminar from Prof. Radu Marculescu

2. Successful Project Review Meeting of European Project Encourage

3. Management Meeting of the TACLe COST Action

4. Another PhD defense which received the highest distinction

5. Work-in-Progress of promising BIC students at CISTER

6. CISTER Researcher Leads Flagship Conference on Architecture of Computing Systems (ARCS 2015)

1. CISTER is involved in the writing of eight ECSEL projects

2. CISTER wins fair-play team medal

3. EMC2 kickoff meeting

4. Arrowhead multi-workpackage meeting

5. One more successful PhD defense

6. CiWork 2014

7. Successful first review of European FP7 project led by CISTER

8. Program Co-Chair of WFCS2014

2. New highly skilled PhD researcher joins CISTER

3. General Chair of the 20th IEEE Real-Time Applications Symposium

4. The largest ICT Artemis project, EMC2, has just started

2. CISTER Participates In A New Project On Validation Of Critical Systems

3. CISTER’s PhD Student Successfully Defends His Thesis

4. CISTER Distinguished Seminar Series Hosts Prof. Sanjoy Baruah

2. New highly skilled Researcher joins CISTER

3. 27th International Conference on Architecture of Computing Systems successfully held in Luebeck

4. CISTER to organize highly reputed Conference on Wireless Sensor Networks: EWSN 2015

2. TACLe COST Action Meeting

3. HiRES Workshop at HiPEAC 2014

4. Arrowhead General Assembly Meeting and first review results

1. ARTEMIS/ITEA co-summit 2013

2. Another ARTEMIS Project approved for 2014

3. Wireless Workshop @Airbus Group

4. ITEA 2 project CarCode meeting

2013

2. P-SOCRATES: FP7 European Project led by CISTER/INESC-TEC Just Started

3. Best Presentation Award at RTNS 2013

4. European Project Proposal To Head For Negotiation Phase

5. CISTER/INESC-TEC Researcher Successfully Defends His PhD

6. New PhD Student at CISTER/INESC-TEC

2. CMU Portugal Working Session "Converting Technology into Products and Services"

3. Arrowhead General Assembly in Lulea

4. Thesis Proposal Defense of CISTER/INESC-TEC Student in the CMU Portugal Program

5. Two new Booklets authored by CISTER/INESC-TEC Researchers

6. Invited Talk at Spanish Real-Time Systems Symposium

7. CISTER/INESC-TEC joins ISEP in the 1st ISEP Alumni Gathering

2. CISTER/INESC-TEC Scores the Best Paper Award at RTCSA 2013

3. CISTER/INESC-TEC Distinguished Seminar Series Hosts Professor José Ramiro Martínez de Dios

4. New researchers arriving to CISTER/INESC-TEC

5. CISTER/INESC-TEC represented at CarCoDe meeting

2. ARTEMIS/FP7 CONCERTO Technical Meeting

3. SENODS Project Evaluation

4. First CISTER Industrial Workshop

5. CISTER hosts SIES’2013, the 8th IEEE International Symposium on Industrial Embedded Systems

1. TACLe Panel Of Experts Workshop On Programming Models For Parallel Architectures

2. CISTER Distinguished Seminar Series hosts Prof. Carlo Fischione

3. Training Workshop On The KALRAY's MPPA

4. PC Co-Chair Of The 26th Int.l Conf. Of Architecture Of Computing Systems (ARCS 2014)

5. ENCOURAGE Project Reaches An Important Milestone

6. ARTEMIS/FP7 CONCERTO Project Kick-Off Meeting

2. CISTER Researcher Leads the Scientific Program of Top-Tier International Conference

3. CISTER on the Spotlights of a Television Science and Technology Dissemination Show

4. Collaboration between CISTER researcher and Canada experts in the spotlight in international workshop

5. CISTER Deeply Involved with 4 New European Artemis/FP7 Project Proposals

6. CISTER to Host a TACle Meeting end of May

7. CISTER Distinguished Seminar Series Hosts Dr. Orlando Moreira

2. SENODs technology is Now Deployed at Portugal Telecom (PT) Datacenter in Picoas, Lisbon

3. High Profile Academics Descend on Porto for the ECRTS'13 TPC Meeting

4. Celebration of the 60th anniversary of Professor Alan Burns

5. Project CarCoDe received approval for funding

2. CISTER Distinguished Seminar Series Hosts Prof. Giuseppe Lipari and Dr. Geoffrey Nelissen

3. Researchers Vincent Nelis and Stefan M. Petters Represent CISTER in Final RECOMP Project Meeting

4. ARTEMIS/FP7 CONCERTO Project to Start in May

5. ARTEMIS ARROWHEAD Project Kickoff Meeting

6. PhD Student of the University of Padova Enrolls with CISTER

1. SENODs on its Way to Large-Scale Deployment

2. CISTER Researcher as an invited speaker in the 3rd TORRENTS Workshop

3. HiRES 2013 co-organised by CISTER Researcher

4. Participation at the Inaugural Symposium for the Phase II of the Carnegie Mellon – Portugal Program

5. Artemis Brokerage Event 2013 receives CISTER Researchers

6. CISTER wraps up European Network of Excellence in Cooperating Objects

7. Expert Seminar on Multicore Enablement for Embedded and Cyber Physical Systems

2012

1. CISTER Researcher receives ACM SIGAda Award

2. CISTER researcher at the Program Chair Meeting of RTAS 2013

4. CISTER Makes a Splash at RTSS 2012

5. CISTER researchers organise the “International School on Cooperating Robots and Sensor Networks”

6. FCT Project PATTERN Recommended for Funding

7. CISTER Distinguished Seminar Series Hosts Prof. Dr.ir. Sander Stuijk and Prof. Dr.-Ing. Jens B. Schmitt

1. CISTER Researcher Vincent Nélis chairs the 6th Junior Researcher Workshop on Real-Time Computing (JRWRTC 2012)

2. Kick-off of EU COST Action TACLe

3. ENCOURAGE plans for the future after a successful first review

4. New Research Scientists at CISTER

5. CISTER Researcher Eduardo Tovar participates in the UBICITEC’s Inauguration Meeting

6. Two CISTER Projects in very good position to be funded by ARTEMIS

7. CISTER Researcher Gurulingesh Raravi wins the JRWRTC’s Best Paper Award

8. CISTER hosts INESC TEC's annual Magusto Party

1. CISTER consolidates collaborative research with top European researchers in Cooperating Objects

2. CISTER Researchers make an impression at EMSOFT 2012

3. CISTER Researchers win Outstanding Paper Award

4. CISTER Researcher Leads Flagship Conference on Real-Time Systems (ECRTS 2013)

5. SENODS Major Milestone

6. Project Manager Gareth Clement joins CISTER

2. Special Issue of the ACM SIGBED Review on the CONET 2012 Workshop

3. New Research Scientist at CISTER

4. CISTER Researchers at the RECOMP Bi-annual Project Meeting

5. CISTER enrolled in 3 ARTEMIS Project Proposals

6. CISTER Researcher’s Internship at the University of Pittsburgh, USA

2. TACLe COST Action approved

3. CISTER co-responsible for the scientific program of successful conference

4. CISTER researcher appointed Program Chair of RTAS 2013

5. IEEE Symposium on Industrial Embedded Systems comes to Porto in 2013!

6. CISTER researcher takes of PhD Committees in Sweden

7. New researchers at CISTER

1. Polytechnic of Porto among the Top-20 Universities in the World

2. The Growing Importance of Real-Time and Embedded Computing

3. CISTER receives recognition at flagship conference

4. CISTER co-organizes 2012 edition of the CONET workshop

5. Special Issue on Cyber-Physical Systems and Cooperating Objects

2011

- ECRTS 2011: World-wide reputed researchers converge to ISEP in the first week of July

- “Excellence and Internationalization in Research” among “Novo Norte” award finalists

- The first RECOMP project week will take place at ISEP

- European Project ENCOURAGE will have the kick-off meeting at ISEP

- CISTER’s increasing visibility and strength leads to 7 new European Consortia

- EWSN/CONET MSc Thesis Award for CISTER’s collaborator

- CISTER hosts the 14th workshop of the Mobile Communication Thematic Network

- What if buildings could autonomously react to climatic changes?

- Roadmap on the emerging domain of cooperating objects

- European ecosystem of collaboration in embedded computing systems meets in Brussels

- CISTER builds partnerships for ITEA projects

- ICT PORTUGAL workshop: New Projects in Networks, Software, Energy and Security

2010

2. The new PT state-of-the-art data centre will include CISTER know-how

3. The largest WSN test-bed in Europe was put together in ISEP

4. Encouraging news for energy-efficiency in buildings

5. CISTER participates in top-level PhD advisory and assessment committees

6. Whishes of a happy season!

2. A new Research Scientist for CISTER

3. CISTER’s researcher Petr Jurcik successfully defended his PhD thesis

4. CISTER participates in ICT 2010

2. 4 new Students choose CISTER for PhD studies

3. CISTER’s new PhD member: Nuno Pereira

4. open-ZB toolset: over 100 000 visits and 6000 downloads!

2. CISTER Researcher gives Keynote Talk at the 16th IEEE RTCSA

3. CISTER to host DEMMON project lab and integrating demonstrator

4. CISTER Distinguished Seminar Series hosts Prof. Tarek Abdelzaher

2. Energy-efficient districts discussed in Barcelona

3. Special Issue on Cyber-Physical Systems and Cooperating Objects

4. Wireless Sensor Networks and mobile robots cooperate in Seville

2. CISTER takes a leading role in ARTEMIS project proposal

3. Ada User Journal finishes the celebration of its 30th Anniversary

4. International Research Cluster meets at CISTER

1. EU-funded project EMMON reaches an important milestone

2. Björn Andersson: world-wide recognized researcher celebrates 5 years with CISTER

3. CISTER Researchers achieve outstanding international recognition

4. CISTER files non-provisional patent in distributed algorithms for Cyber-Physical Systems

1. CISTER: At the Forefront of Research in Portugal since 2004

2. We Take on New Goals and Bigger Challenges: upgrading to CISTER 3.0

3. CISTER to Host Next General Meeting of the European Network of Excellence CONET

1. CISTER starts participation in one of the largest R&D projects in EU: RECOMP

2. CISTER attracts 4 additional international PhD students

3. New Project with one of the top US Universities: REJOIN

4. CISTER shows its international strength by taking part in 3 new ARTEMIS Consortia.